Featured Capabilities

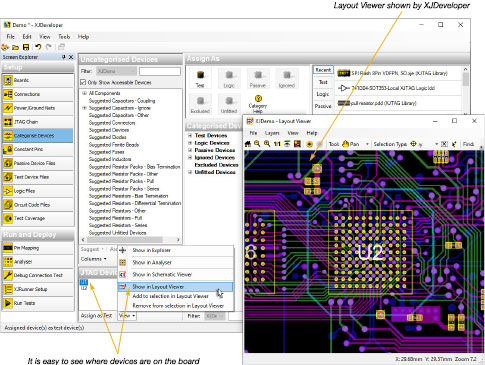

Layout Viewer

Introduction

The Layout Viewer allows you to quickly find the physical location of components, nets and pins on a board. It provides the capability to view layout design data extracted from the ODB++ data through interfaces in XJDeveloper, XJInvestigator and XJRunner.

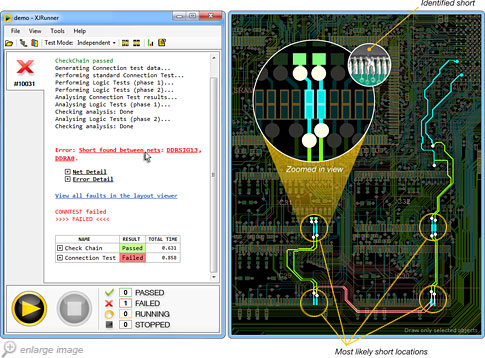

You can use the Layout Viewer to visualise any faults that are found when running tests. The Connection Test output includes clickable links to directly display all of the relevant circuit elements. XJEase tests can also output links to display devices, pins and nets in the circuit layout.

Key Benefit

- Improve productivity by visualising the exact location of faults to be repaired

Features

- Aids identifying likely points of failure.

- Measures distance between objects.

- Control over which layers are visible.

- Advanced layer and zoom controls.

- Exports graphics to the clipboard, a file or printer.

- Import pictures for clearer display

Included with XJDeveloper, XJInvestigator and XJRunner

The Layout Viewer is integrated into XJDeveloper, XJInvestigator and XJRunner to help engineers quickly identify faults.

Visualise circuit elements

The advanced graphical display highlights selected components and nets. Individual layers can be turned on or off as required to make it easy to see specific circuit elements.

Determine the location of faults within seconds

The Layout Viewer can be used to quickly locate where faults are on the board under test.

The test output provides details about the types of fault and which nets are involved. There are also clickable links that allow the fault to be easily visualised in the Layout Viewer. By showing the routing of nets, the Layout Viewer helps to locate the fault on the physical board by showing the potential problem areas.

In this particular example, XJRunner reports that Connection Test has failed, and has identified two nets that are shorted together. By looking at the layout, it is easy to determine that the four most likely locations are the pads on the memory devices. It is unlikely that the fault is under the BGA device as the pins are not next to each other.

By examining the four locations on the board, it was quickly identified that the problem was a soldering fault on IC31.

Import board pictures

For even more help in identifying where on a board the faults are located, pictures of the front and the back of the board can be imported. These images can then be displayed behind the CAD data with its highlighted components and nets.

For support, or for a quote on any part of the XJTAG system, please contact us.

Configure your products