XJTAG DFT Assistant for OrCAD Capture

Free ‘Design For Test’ (DFT) plugin to reduce board re-spins

The new XJTAG® DFT Assistant for OrCAD® Capture software plugin allows design engineers to identify and correct potential JTAG testability problems early in the design cycle. Because many IC packages are inaccessible for testing using physical probes, failure to provide JTAG test access to these chips could result in a board re-spin and an expensive project delay.

XJTAG DFT Assistant helps you validate the correct implementation of boundary scan chains*, as well as provides compliance to ‘Design For Test’ best practices. What’s more, JTAG compliance can also unlock a range of other benefits for your board, which include faster prototype debug and device programming, as well as faster and more cost-effective manufacturing testing.

* Designers are not required to understand the underlying JTAG boundary scan technology to be able to use the plugin.

XJTAG Chain Checker

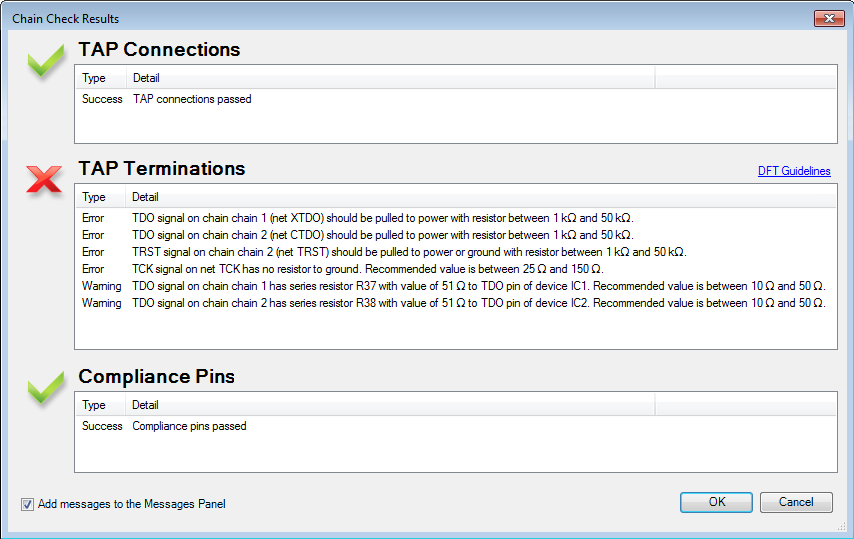

After a quick 4-step board setup, the XJTAG Chain Checker feature analyses the netlist and finds a routable scan chain. It also offers a unique DFT feature: checking that the TAP signals are correctly terminated.

XJTAG Chain Checker identifies potential errors and warnings found on JTAG chains, including:

- Connection errors if any of the JTAG Test Access Point (TAP) signals are connected to the wrong pin(s) on a JTAG-compliant IC.

- Termination warnings if any of the TAP signals are not terminated as recommended.

- Compliance pin errors if they are incorrectly pulled high or low, or are left floating.

XJTAG Access Viewer

The XJTAG DFT Assistant extension also identifies the extent of JTAG access across an entire schematic. This is overlaid directly onto the schematic using the XJTAG Access Viewer feature, allowing you to understand your test coverage at an early stage in the design. You can highlight the nets individually on the schematic by JTAG access, to show: read, write, power/ground and no access.

By visualising the extent of JTAG access, you can easily see which components are accessible using boundary scan and where changes need to be made to extend test coverage further.

Features

- Fully integrated into Cadence® OrCAD Capture (v17.2 or higher)

- Easy assisted board setup to carry out a JTAG DFT analysis

- Automatic import of netlist from Cadence OrCAD Capture

- Includes a JTAG Access Viewer that overlays testable nets directly on the schematic diagram

- Analysis of results from the XJTAG Chain Checker tool clearly identifies potential errors in the chain(s)

- Provides three categories of errors: connection, termination and compliance

- Shows testable nets using colour-coded connections

- Assisted categorisation of logic and passive devices, to extend scan chains

- Export projects for further test development using XJDeveloper

Download free DFT Assistant plugin

also available for other EDA tools

Configure your products