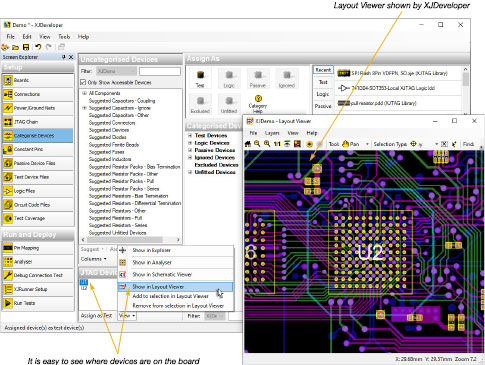

Mit dem Layout Viewer können Sie schnell den physischen Standort von Komponenten, Netzen und Pins auf einer Leiterplatte ausfindig machen. Er bietet die Möglichkeit, Layout-Design-Daten aus ODB++-Aufträgen in XJDeveloper, XJInvestigator und XJRunner betrachten zu können.

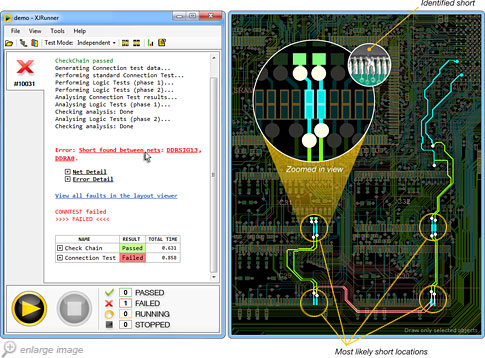

Sie können den Layout Viewer verwenden, um alle Fehler zu visualisieren, die beim Ausführen von Tests gefunden werden. Die Verbindungstest ausgabe enthält anklickbare Links, um alle relevanten Schaltungselemente direkt anzuzeigen.

Layout Viewer Produktblatt XJDeveloper XJRunner

Wesentliche Vorteile

- Steigern Sie die Produktivität, indem Sie die genaue Lage der zu reparierenden Fehler visualisieren

Features

- Hilfsmittel, die mögliche Fehlerpunkte identifizieren

- Misst den Abstand zwischen den Objekten

- Kontrolle über Sichtbarkeit der einzelnen Schichten

- Erweiterte Layer- und Zoom-Bedienelemente

- Exportiert Grafiken in die Zwischenablage, eine Datei oder zu einem Drucker

- Importiert Bilder für klarere Anzeige

In XJDeveloper, XJInvestigator und XJRunner kostenlos enthalten

Der Layout Viewer ist in XJDeveloper, XJInvestigator und XJRunner integriert, um Ingenieuren zu helfen, Fehler schnell zu erkennen.

Visualisierung von Schaltungselementen

Die erweiterte grafische Darstellung markiert ausgewählte Komponenten und Netze. Einzelne Schichten können nach Bedarf ein- oder ausgeschaltet werden, um die Betrachtung bestimmter Schaltungselemente zu vereinfachen.

Bestimmen Sie die Fehlerposition innerhalb von Sekunden

Der Layout Viewer kann verwendet werden, um schnell zu lokalisieren, wo sich Fehler auf der Leiterplatte befinden.

Die Textausgabe von XJRunner gibt Auskunft über die Arten von Störungen und welche Netze betroffen sind. Weiterhin stehen anklickbare Links zur Verfügung, mit denen der Fehler im Layout Viewer leicht sichtbar gemacht werden kann. Durch die Darstellung des Routings von Netzen hilft der Layout Viewer, den Fehler auf der physischen Karte zu lokalisieren, indem er mögliche Problembereiche anzeigt.

In diesem speziellen Beispiel berichtet XJRunner, dass der Verbindungstest fehlgeschlagen ist und hat zwei Netze identifiziert, die zusammen kurzgeschlossen sind. Durch das Betrachten des Layouts ist leicht zu bestimmen, dass die vier wahrscheinlichsten Orte die Pads auf den Speichergeräten sind. Es ist unwahrscheinlich, dass der Fehler unter dem BGA-Gerät liegt, da die Stifte nicht nebeneinander liegen.

Durch die Prüfung der vier Standorte auf der Leiterplatte konnte schnell erkannt werden, dass das Problem ein Lötfehler auf IC31 war.

Importierung von Leiterplatten-Bildern

Für noch mehr Hilfe bei der Identifizierung der Stelle einer Leiterplatte, an der die Fehler zu lokalisieren sind, können Bilder von der Vorderseite und der Rückseite des Boards importiert werden. Diese Bilder können dann hinter den CAD-Daten mit den hervorgehobenen Komponenten und Netzen angezeigt werden.

Für Support oder ein Angebot für jegliche Produkte des XJTAG-Systems, zögern Sie bitte nicht, Ihren lokalen Vetriebspartner zu kontaktieren.