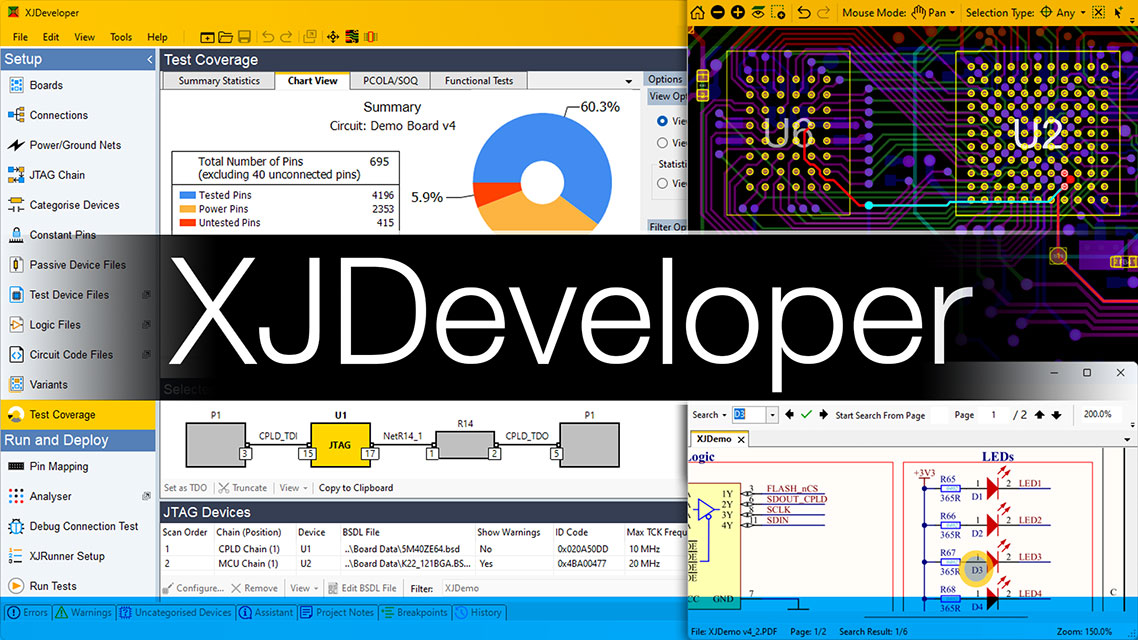

XJDeveloper — Entorno de desarrollo completo (IDE)

XJDeveloper permite desarrollar rápidamente y ejecutar los tests JTAG y las rutinas de programación.

Un test de conexiones generado automáticamente, combinado con tests para componentes no-JTAG tales como RAM, testeará las tarjetas PCB en busca de cortocircuitos y circuitos abiertos. Memorias Flash y EEPROMs pueden ser programadas también, así como componentes JTAG como CPLDs, FPGAs e incluso Flash internas en procesadores que tengan un interfaz de depuración JTAG. Incluso antes de tener el hardware, el informe de la cobertura de test del XJDeveloper permite revisar fácilmente qué porcentaje de la tarjeta PCB será testeado.

- Rápido desarrollo y depuración de test

- Setup de programación in-situ (ISP)

- Análisis de cobertura de pruebas

- Librería de componentes no-JTAG

Beneficios clave

- Reduce el tiempo empleado en depurar PCBs

- Mejora el tiempo de comercialización y reduce el riesgo de fallos en el proyecto gracias a una temprana verificación en el diseño

- Reduce el tiempo de desarrollo de test reutilizando tests de los prototipos/diseños en fabricación y trabajos de campo

- Ahorro continuo de tiempo gracias a la reutilización de tests en todos los proyectos

Opciones de licencia flexibles

- Licencia de hardware

– se mantiene en el controlador JTAG esta manera puede utilizar XJTAG en cualquier número de ordenadores - Licencia de red

– se mantiene en un servidor de licencias en red disponibles desde cualquier lugar del mundo

Rápido desarrollo de test

El XJDeveloper ayuda a acelerar el desarrollo de test haciendo sugerencias de cómo categorizar los componentes y las pistas en el circuito. Si se tiene la información de la lista de materiales (BOM), también será sugerido qué modelo de las librerías instaladas se debería utilizar para cada componente.

Las librerías contienen modelos para componentes pasivos simples como resistencias, circuitos integrados (C.I.) complejos como son las memorias DDR3 y componentes que pueden ser descritos utilizando tablas de verdad como buffers y puertas lógicas.

Utilizando estos modelos, puede ser creado un completo sistema de test funcional sin programación extra.

Potente lenguaje de test y librería instalada

El XJEase (lenguaje de programación de alto-nivel del XJDeveloper) proporciona toda la funcionalidad, flexibilidad y control que son necesarios para hacer el test de los componentes no-JTAG en los circuitos.

La librería instalada del XJEase contiene tests para miles de componentes, pero también es fácil escribir nuevos tests con el XJEase incluso si no se tiene ninguna experiencia con el software.

Los tests son escritos en términos del componente que está siendo testeado, así sólo se necesita describir en qué pines del componente no-JTAG se debería envíar señal y cuáles deberían ser leídos. El XJEase averiguará qué parte de la cadena JTAG necesita ser controlada y monitorizada para implementar todos los requerimientos.

Esto no solo hace el desarrollo de test más rápido, también permite reutilizar los tests para cualquier caso de ese tipo de componente en cualquier circuito.

Utilizando las características del lenguaje de alto-nivel tales como variables, bucles, ejecución condicional, llamadas a funciones, etc… es posible interactuar con la tarjeta PCB en tiempo real, no sólo estableciendo y comprobando valores. He aquí un ejemplo del código XJEase.

El depurador XJEase cuenta con una ventana de variables para hacer seguimientos y puntos de interrupción para ayudar a conseguir que los tests se ejecuten lo más rápido posible.

Test de conexiones

El XJDeveloper tiene un test de conexiones incorporado para todos los pines boundary scan disponibles en los componentes JTAG. Este test verifica cortocircuitos y circuitos abiertos, incluyendo cortos a tierra o a alimenta-ción, cortos resistivos y cortos invertidos. Las resistencias pull-up y pull-down también son verificadas.

Como parte de su funcionalidad, el test de conexiones también testea dinámicamente las señales de datos y de control en componentes lógicos tales como buffers y puertas lógicas.

Cuando el fallo es detectado, el test de conexiones genera tests más específicos para investigar y localizar dónde se encuentra el error, usando el Schematic Viewer y el Layout Viewer.

Testeando componentes no-JTAG

El XJDeveloper hace fácil el utilizar componentes en la cadena JTAG para verificar las conexiones de los componentes no-JTAG. Por ejemplo, escribiendo valores de test a un chip de memoria y leyéndolos de vuelta, se puede verificar que los datos y las líneas de direccionamiento están libres de errores – sin tener que poner en marcha el procesador. Tests avanzados, como envíar y recibir paquetes Ethernet, permiten incluso testear partes de la PCB que no tengan acceso JTAG.

Importación de datos estándar

El XJDeveloper utiliza las netlists y los archivos BSDL (Lenguaje de Descripción Boundary Scan) para hacer el test de las conexiones alrededor de los componentes JTAG. Más de 80 formatos de netlists son soportados actualmente. Un formato, ODB++, también proporciona información del diseño que puede ser utilizada para mostrar la localización física de los fallos.

Programando memorias Flash y componentes JTAG

Los archivos de memoria Flash en la librería del XJEase incluyen toda la funcionalidad requerida para programar la Flash con una imagen. Para programar muchos componentes JTAG, como CPLDs y FPGAs, el XJDeveloper permite ejecutar archivos STAPL/JAM o SVF generados desde las herramientas del fabricante del componente. La Flash interna en algunos procesadores puede también ser programada a través del interfaz de depuración JTAG.

Análisis de la cobertura de test

Tan pronto como se tenga una netlist y un esquema, se puede crear un proyecto con el XJDeveloper y verificar el nivel de la cobertura de test; esto es calculado automáticamente combinando la cobertura obtenida a través del test de conexiones y el test de los componentes no-JTAG hecho con el XJEase. Se puede descargar la guía de referencia del “Design For Test” de XJTAG que cubre muchas de las cuestiones involucradas en la realización de test boundary scan en su pleno potencial.

XJRunner, Analyser, “Schematic Viewer” y “Layout Viewer” integrados

Los tests pueden ser depurados utilizando el interfaz XJRunner integrado antes de ser enviados a la fábrica. También están integrados el visualizador de esquemas “Schematic Viewer” y el visualizador de diseños “Layout Viewer” que permiten encontrar rápidamente cualquier pista o componente en el circuito al desarrollar los tests o tratando de localizar un fallo.

No hay netlist? Ningún problema!

Incluso si no se tiene netlist para la tarjeta PCB que se quiere testear, todavía se puede utilizar el XJDeveloper. La característica “no-netlist testing” permite crear un sistema de test con XJDeveloper directamente sólo desde archivos BSDL. El sistema puede aprender automáticamente las conexiones entre los componentes JTAG habilitados y se pueden añadir manualmente componentes no-JTAG, como RAM y Flash, para incrementar la cobertura de test.

Integración

Los test desarrollados en XJDeveloper pueden ser integrados en NI LabVIEWTM utilizando los editores visuales (VIs) instalados. También pueden ser desarrollados ejecutores de test hechos a medida en Visual Basic®, C#®, etc… utilizando el interfaz .NET.

Desarrollo de test

Si todos los ingenieros están ocupados, XJTAG también ofrece un servicio de consultoría para crear los sistemas de test con XJDeveloper o los archivos de componentes hechos exactamente a la medida de sus requerimientos.

Características

- Test de conexiones adaptativo integrado

- Soporte lógico automático

- Librerías integradas de piezas estándar

- Reutiliza cualquier test que se haya escrito

- Programación de componentes: Ej. bucle cerrado en comunicaciones Ethernet

- Análisis de la cobertura de test antes de proceder a hacer el diseño de la PCB

- Visualizadores de esquemas y diseños de tarjetas PCB integrados

- Test avanzado: Ej. bucle cerrado en comunicaciones Ethernet

- Integración con ejecutores de test estándar o aplicaciones personalizadas

- Más de 100 formatos de netlists soportados, incluyendo ODB++, RINF, Protel, PADS-PCB y ALLEGRO

- Habilidad para testear tarjetas PCB sin netlists – sólo utilizando archivos BSDL

- Layout Viewer

- Schematic Viewer

- Waveform Viewer

- Integración

- Test de componentes 1149.1 y 1149.6

Para obtener más información, por favor, póngase en contacto con su distribuidor local.

¿Listo para empezar?

¡Ver XJTAG en acción!

Nuestros expertos estarán encantados de mostrarle cómo las herramientas XJTAG pueden ayudarle a diagnosticar fallos en su placa, así como a reducir el tiempo de desarrollo de tests y reparaciones.

¿Tiene preguntas? ¡Contáctenos!

Envíenos un mensaje y uno de nuestros especialistas en tests se pondrá en contacto con usted lo antes posible.