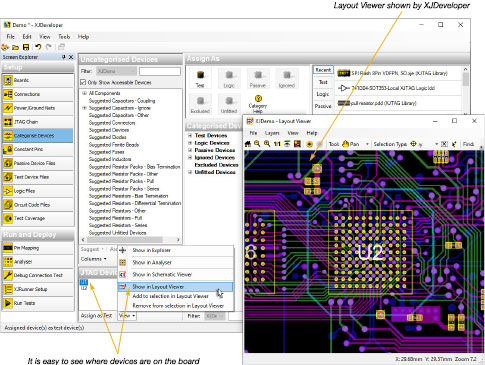

Layout Viewer により基板上の部品やネット、ピンの物理的な場所を即座に特定。ODB++ ジョブから抽出されたレイアウト設計データの表示をするこの機能は、XJDeveloper、XJInvestigator と XJRunner の両方で活用いただけます。

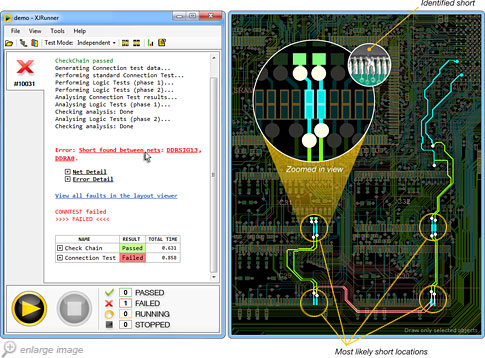

Layout Viewer によりテスト実行時に見つかったあらゆる欠陥をビジュアル表示。Connection Test の結果出力に含まれるリンクをクリックすることで、関連する全ての回路エレメントをダイレクトに表示します。

Layout Viewer データ資料 XJDeveloper XJRunner

主な効果

- 修正が必要な欠陥箇所の的確なビジュアル表示で解析作業を支援

機能

- 欠陥箇所の特定を支援

- 対象物間の距離を測定

- 表示するレイヤーを制御

- 高度なレイヤーとズームの制御

- グラフィック表示を、クリップボード、ファイル、プリンタにエクスポート

- 製造担当者向けに基板写真をインポート

XJDeveloper、XJInvestigatorとXJRunner に標準装備

欠陥箇所の特定を直ちに行えるLayout Viewerは、XJDeveloper、XJInvestigator と XJRunner に標準装備しています。

回路エレメントの可視化

高度なグラフィカル表示で、選択された部品やネットをハイライト表示。個々のレイヤー表示をオン・オフさせて、特定の回路エレメントを見ることも簡単です。

欠陥箇所を直ちに特定

Layout Viewer により、テスト対象基板の欠陥箇所を素早く特定することができます。

XJRunner のテスト結果(テキスト形式)から欠陥のタイプや関連するネット情報が得られます。そしてリンクをクリックするだけで、欠陥箇所をLayout Viewer に表示。 Layout Viewer で欠陥を含んだネット経路を視覚的に確認すれば、問題の特定も容易です。

以下の例では XJRunner による Connection Test に失敗があった相互に短絡している2つのネットが特定されています。ここでレイアウトを確認することで、メモリーデバイス上の4箇所のパッドが最も可能性 が高いことが容易に判断できます。例えばBGAデバイス部分(図右上)では、これらネットのピンが隣り合っていないことが見えるので、欠陥の可能性は低い と判断することができます。

そして基板上の4箇所を詳しく調べることで、IC31のハンダ不良に問題があることを直ちに判明しました。

基板写真のインポート

基板上の欠陥箇所を特定するために、基板表面と裏面の写真をインポートして活用することもできます。これらのイメージは、部品やネットをハイライト表示しているCAD データの後ろに表示されます。