FPGA、CPLD、および殆どの32ビットマイクロプロセッサに搭載される「バウンダリスキャン」機能が提供する利点は、もはや無視することはできなくなりました。バウンダリスキャンにより、PCBの製造不良を迅速かつ容易にチェックできることの重要性が高まり続けています。特にBGAは、他の試験技術を用いてはんだ付け不良をチェックするのが非常に困難で時間がかかるためです。

バウンダリスキャンテストの恩恵をすでに受けている世界中のエンジニアはBSDL(Boundary Scan Definition Language)ファイルをダウンロードなどで入手するはずです。またSVF(Serial Vector Format)コマンドに遭遇することもあるでしょう。 通常、ユーザーはこれらファイルの複雑さを知る必要は殆どありません。ただ、その内容とバウンダリスキャンテストで果たす役割を知ることで、そのようなテストを実行するために必要なファイルへの、より良い理解に役立つこともあるでしょう。

この記事ではBSDLとSVFファイルの概要を説明し、それらの基本的な機能と特徴を説明してそれらの重要性を紹介します。

バウンダリスキャンテスト

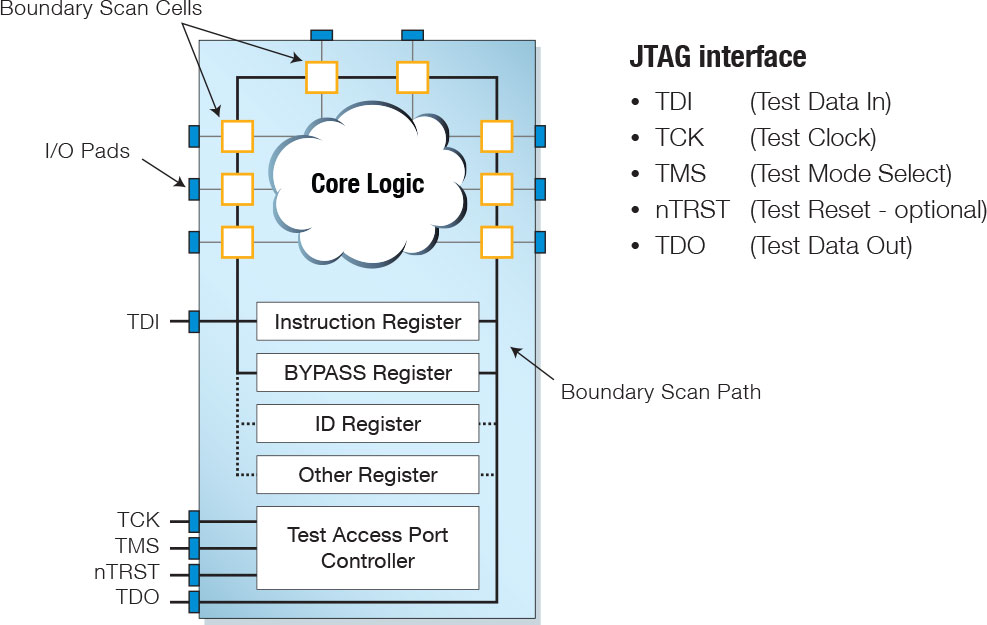

バウンダリスキャンテストは、JTAG対応デバイスの内部アーキテクチャを使用してピンを制御します。Figure 1に示すように、「バウンダリスキャンセル」はデバイスの通常のコアロジックとパッケージのピン(またはBGAボール)の境界上にあります。これらのセルにより、電源ピン以外を内部機能(Core Logic)から分離し、基板のJTAGコネクタに接続されたプローブHWを介して、ホストPCから値の設定や読み取りを行います。

Figure 1 – Boundary Scan Architecture

PCにインストールされたソフトウェアは、デバイスをバウンダリスキャンテストモードにして、入念に選択されたテストパターンを各ピンに適用します。 次にバウンダリスキャンセルは実際の出力と、その結果として他のピンへの入力を記録して、それら結果は解析のためにPC上のソフトウェアに送信されます。 このようにして実装された各ピンがプローブの役割を果たし、断線、短絡、またはスタックの障害が発生しているネットを特定することや、重要なデバイスが正しく配置されていて動作可能であることを確認します。

基板上のソフトウェアを起動して実行することや、チェック対象のピンに物理的にプローブアクセスする必要はありません。

バウンダリスキャンモードでは、TMS信号がデバイスのステートマシンを操作して内部テストロジックの動作を制御しながら、テストパターンと命令がTDIピンへシリアルに入力されます。

JTAGに対応するICは、命令レジスタ(実行されるバウンダリスキャン命令を保持)といくつかのデータレジスタ、バイパスレジスタ(バウンダリセルをバイパスさせる)と、IDレジスタ(デバイスを識別)を持ちます。 一連のバウンダリセルはまとめて「バウンダリスキャンレジスタ(boundary scan register)」と呼ばれます。

ステートマシンは、さまざまな状態間でステップ実行され、これらのレジスタに情報を設定することや取得することができます。命令レジスタはどのデータレジスタが作用するかを定義します。 バウンダリスキャンアーキテクチャ、命令、およびステートマシンの詳細は、IEEE 1149.1規格によって定義されています。

ファイルの必要性

テストソフトウェアがバウンダリスキャンモードでデバイスを制御できるようにするには、JTAG対応デバイスの製造元がどのようにアーキテクチャを実装したかに関する情報が必要です。 BSDLファイルはこのデータを提供します。通常は製造元のWebサイトからダウンロードできます。 このファイルがなければ、バウンダリスキャンテストを実行することは不可能です。またデバイス製造元は、IEEE 1149.1への準拠を主張するために、このファイルの提供が必要です。

対照的に、SVF(Serial Vector Format)ファイルは、ベンダーやプラットフォームに依存することなく、特定のテストに使用されるステートマシンの遷移と付随するビットパターンのシーケンスを記録する1つの方法です。バウンダリスキャンテストを実行するために必要ではありませんが、XJTAGのXJDeveloperなどのツールはSVFファイルに対応していて、それらが定義するルーチンを実行することができます。バウンダリスキャンはデバイスのプログラミングにも使用できるため、デバイス製造元のツールの多くは、プログラミング用にSVFファイルを出力します。

これら両方のファイルは、ASCIIテキストフォーマットで作成されており、情報を読んで理解することや、さまざまなベンダーのツール間で自由に転換することができます。

BSDLファイルの中身

BSDLファイルは、VHDL(Very high-speed integrated-circuit Hardware Description Language)の構文と文法をベースにしています。 それらは、規格で定義されていないバウンダリスキャン実装の側面を記述しています。例えば、命令レジスタの長さ(デバイス製造業者によって設定される)は提供しますが、IDレジスタの長さ( 標準では32ビット長と規定)は定義されません。 どのバウンダリスキャンセルがどのピンに接続されているか、さまざまなレジスタの詳細、およびバウンダリスキャンセル自体の説明が表示されます。

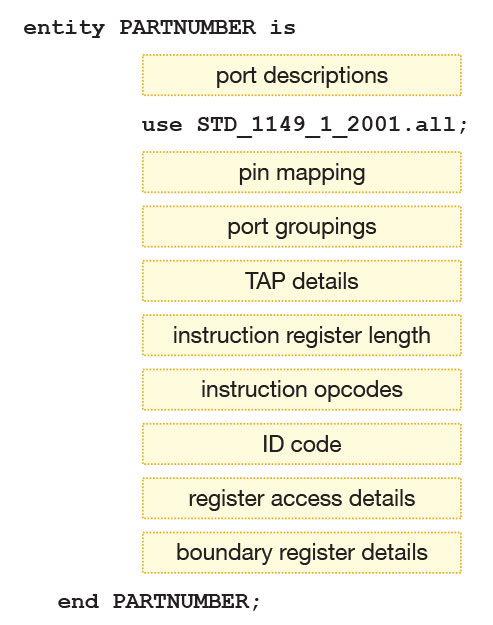

Figure 2はBSDLファイル内の主な要素です(わかりやすくするために全ての機能は表示していません)。

Figure 2 – Main elements of a BSDL file

Port Descriptionsポートの説明:

BSDLファイルのこのセクションには、デバイス上のすべての接続についての説明があります。 この段階では、ここで作成した定義を変更せずにさまざまなピン配置に再利用できるように、ピン番号ではなくシンボル名を各ポートに与えます。 デバイスの物理ピンと各ポートのマッピングはファイルの後半で行われます。

バウンダリスキャンに使用できるポートは、入力、出力、双方向、またはバッファのいずれかとして説明されています。 ポート名は複数の信号のグループを表す場合があるため、ディメンションも指定されます。ポートが単一のシグナルで構成されている場合、ディメンションは「bit」として与えられ、複数の場合には信号の数を表す数字とともに“ bit_vector”として表されます。この命名法は、相互接続された電源ピンまたはグランドピンにも使用できます。 ポートの記述例は、「CE:in bit;」や「EXTBUS: out bit_vector (1 to 8);」です。

電源ピンやアナログピンなど、バウンダリスキャンに使用できない接続は「LINKAGE」として定義されます(2013規格より前に作成されたBSDLファイルでは)。

2013年版以降の規格に準拠したデバイスでは、これらのピンが区別されます。たとえば、電源ピンは「POWER_NEG」と定義され、アナログピンは「LINKAGE_OUT」と定義されます。

Pin Mappingピンマッピング:

PIN_MAP属性は、各ポートのシンボリック名をパッケージ上の物理的な接続にマッピングし、接続されないピンは識別されます。 たとえば、ピン1にCE、ピン2にVOUT、ピン3にGNDを割り当てるには、ピンマッピングを実行するテキスト文字列に「…CE: 1, VOUT: 2, GND: 3…」と入力します。

Port groupingsポートのグループ化:

1ビットのデータを伝送するために複数のピンが必要な場合(たとえば差動信号が使用される場合など)、各ペアを構成するポートはPORT_GROUPING属性を使用してグループ化されます。 また電圧信号か電流信号かを指定します。

TAP Details (Test Access Port) TAPの詳細(テストアクセスポート):

TAP(Test Access Port)はJTAG信号のセットに付けられた名前(スキャンポートとも呼ばれる)で、これらの信号に使用されているポート名をテストツールに指示する属性のセットが、BSDLファイルに含まれています。 TCK用のポートが定義されると、その保証最大周波数(Hz)も、安全に停止することができる論理状態の詳細と共に提供されます。

Instruction Register Details命令レジスタの詳細:

命令レジスタの長さはデバイス間で異なる可能性があるため、BSDLファイルにその長さを記述する必要があります。これはINSTRUCTION_LENGTH属性を使用して定義します。

Instruction Register Opcodes命令レジスタのオペコード:

オペコードは、特定のバウンダリスキャン動作を実行するために命令レジスタで必要とされるバイナリシーケンスに与えられる名前です。 IEEE 1149.1規格では、BYPASS[1]命令にすべて“1”からなるオペコードを含める必要があると規定されていますが、他のオペコードは定義されておらず、製造元は自由に設計に適したコードを選択できます。(規格の以前のバージョンでは、EXTEST[2]はすべて“0”でなければならないと規定されていましたが、スタックの障害がTDIを低く保持している場合、問題の可能性があるため、オールゼロのオペコードはもはや推奨されません)したがって、製造元は各コマンドにどのバイナリコードが選択されているかに関する情報を提供する必要があります。このオペコードリストはBSDLファイルで提供されます。

属性文字列の抽出例は「…SAMPLE[3](0010), EXTEST(0010)…」です。 BYPASSは標準で定義されているため、文字列に含める必要はありませんが、製造元はよくそうします。

損傷する危険性があるために実行するのが潜在的に危険であるオペコードもリストされ、回避されるようにします(このようなオペコードは「プライベート」命令として識別されます)。

[2] EXTEST命令は、TDIとTDOの間にバウンダリセルを挿入し、入力されたデータがデバイスのピンの状態を制御できるようにします。

[3] SAMPLEは、TDIとTDOの間にバウンダリセルを挿入しますが、デバイスを通常の動作モードのままにして、デバイスに出入りする機能データを監視できるようにします。

ID Code IDコード:

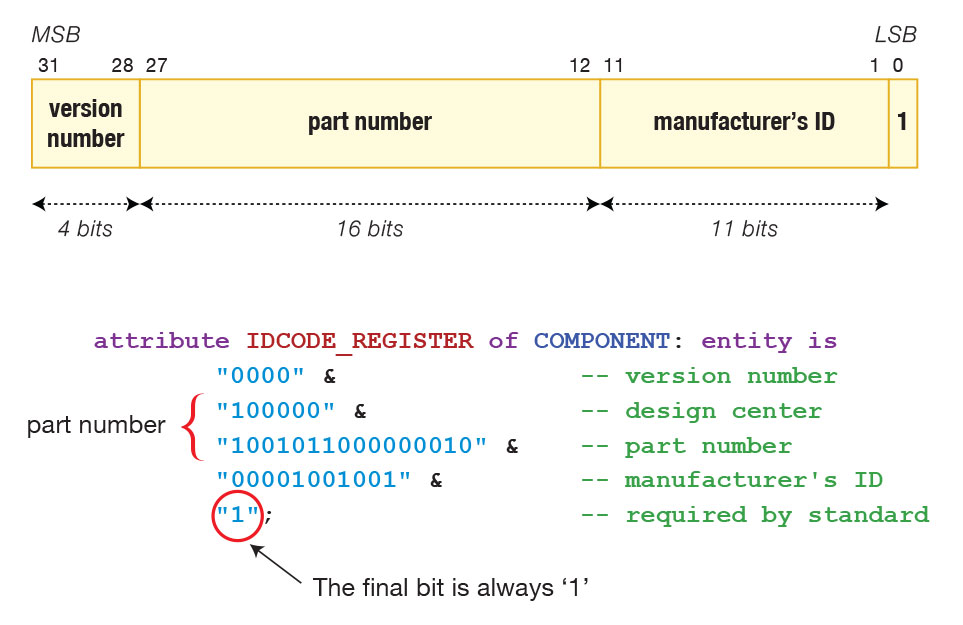

バウンダリスキャンデバイスにIDレジスタ(製造元、部品番号、およびシリコンバージョンに関する情報を提供する)を含めることは必須ではありませんが、これが実装されている場合、ICのBSDLファイルには一致するデータが含まれます。 これはIDCODE_REGISTER属性を使用して定義されます。この属性には、通常わかりやすいようにコメント付きでフォーマットされたテキスト文字列が含まれています。 Figure 3に、IDコードの記述形式とBSDLファイルからの典型的な抜粋を示します。

バウンダリスキャンテストの開始時に、ソフトウェアはこの情報をデバイス内の値と照合します。 それらが一致しない場合、エラーが報告されテストは中止されます。

Figure 3 – An example of an ID Code structure

Register Access Descriptionsレジスタアクセスの詳細:

BSDLファイルのこのセクションには、JTAG命令ごとにTDIとTDOの間に配置されるレジスタを定義します。 たとえば、文字列 “BYPASS(HIGHZ, CLAMP)”は、HIGHZ命令またはCLAMP命令が実行されたときにBYPASSレジスタが選択されることをツールに通知します。

Boundary Register Descriptions境界レジスタの詳細:

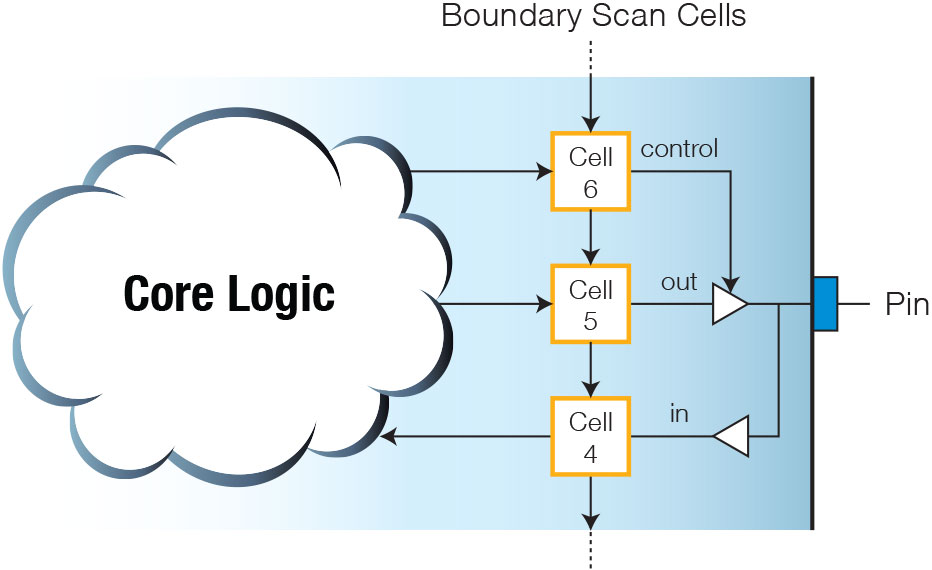

バウンダリセルの集合は「バウンダリレジスタ」と呼ばれ、BSDLファイルに詳細が記述されています。 ファイルにより、含まれているセルの総数を(BOUNDARY_LENGTH属性を使用して)指定した後、使用されるさまざまなタイプのセルの識別が続行されます。 Figure 4は、1つのピンのバウンダリセルの一般的な構成を示し、ピンが複数のバウンダリセルに接続する方法を示しています。この例では、一方のセルに制御ビット、もう一方のセルに設定する出力、もう一方のセルに読み取った入力値を格納します。

Figure 4 – An example of Boundary Register Cells

BSDLファイルは、レジスタ内の各セルについて、そのシンボル名を使用して接続先のポートをリストし、セル自体とその使用方法を記述します。各エントリには次の情報が含まれます。

- The type of cell. セルのタイプ バウンダリセルには多くの設計があります。単純なものはデータのキャプチャのみが可能で、他のセルはより普遍的でピンの更新と監視ができます。 クロック入力など、監視するピンが容量性負荷に特に敏感な場合は、よりシンプルなセル設計が必要になる場合があります。 IEEE 1149.1規格では、BC_0〜BC_10を指定する11種類のセルタイプを定義しています。 IEEE 1149.6規格(AC結合信号をカバーするためにバウンダリスキャンを拡張)では、AC_0からAC_10の指定子が追加されています。

- The relevant port 関連ポート は、シンボリック名を使用して接続されます。

- The function of the cell: セルの機能:これは特定のセルがどのように使用されているかを示します。 IEEE 1149.1では、INPUT、CONTROL、CLOCK、および2種類の出力を含むいくつかの機能が定義されています:OUTPUT2(ハイおよびロー状態のみで出力を駆動するセル用)およびOUTPUT3(トライステート出力用)。Figure 4の例では、セル6がコントロールセルとして使用されているのに対し、セル4は入力として使用されています(両方のセルは同じデザインです)。

- The “safe bit” value:「安全ビット」値:これは、そうでなければ未定義となる場合にセルにロードされるべき論理値を示します。 問題にならない場合は、値を「X」に設定できます。

- セルの出力を無効にできる場合(Figure 4の例のセル5など)、どのセルが制御ビットを提供するか、どの論理レベルで出力が無効になるか、およびそのときに何が起こるかを識別する追加情報や、ディスエーブルされたときにその出力はどうなるか(たとえば、内部プルアップまたはプルダウンがあるか、それともハイインピーダンスになるか)といった情報が提供されます。

Figure 4の例では、定義は次のようになります(バウンダリレジスタ内の他のセルは無視されます)。

6 (BC_1, *, CONTROL, 0),

5 (BC_1, PINNAME, OUTPUT3, X, 6, 0, PULL1),

4 (BC_1, PINNAME, INPUT, X);

BSDLファイルには、使用されているセルデザインに関する情報を含むVHDLパッケージを呼び出す「use」ステートメントが含まれています。

IEEE規格にリストされているセルタイプはSTD_1149_1_2001のような標準パッケージに記述されており、 “use STD_1149_1_2001.all” ステートメントによってBSDLファイル内から呼び出されます。 これらのファイル名は、それらが参照するパッケージのエディションを示します(1994、2001、2003など)。 IEEE 1149.6をサポートするデバイス用のファイルには、AC結合をサポートするセル用のパッケージファイルを呼び出すための追加のuseステートメントがあります。

Figure 2からわかるように、これらのステートメントはファイルの早い段階に存在します。

Custom Cell Type Package Files カスタムセルタイプパッケージファイル:

製造元が標準パッケージで定義されているものとは異なるセルの実装が必要なこともあります。その場合、BSDLファイルには、データをファイルに直接含めるか、より一般的には別のVHDLパッケージファイルへの呼び出しを追加することによって、そのようなカスタムセルに関する情報を含めます。カスタムセルパッケージファイルは、標準セルと同じ方法で呼び出されます。たとえば、ファイルMyPackageを呼び出すには、「use MyPackage.all」という文を入力します。

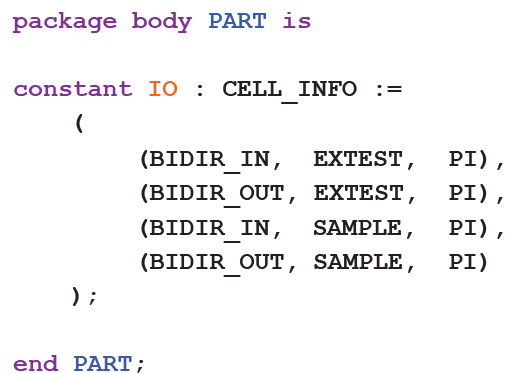

セルはさまざまな方法で使用できるため、カスタムセルパッケージには、各使用モードでさまざまなコマンドにどのように応答するかを説明するために、セルごとに複数の情報が含まれています。 たとえば、入力として使用した場合、EXTESTが実行されたときに何をするのか。 同一のコマンドが実行されたがセルが出力として使用されている場合、同じセルは何をするのか。 この情報はすべてカスタムセルタイプパッケージに取り込まれます。 Figure 5は、セルの定義から抜粋したものです。

Figure 5 – Extract from a Custom Cell Type Package

Capacitively Coupled Signals容量結合信号:

デバイスが容量結合デジタル信号をサポートし、IEEE 1149.6に準拠している場合、そのBSDLファイルにはAC機能を持つセルに関する追加情報が含まれます。 AIO_Pin_Behaviour属性が使用され、どのピンが機能をサポートしているか、そして適切であれば、どのセルを使用してAC動作を無効にできるかをリストした文字列が含まれます。 たとえば、ポートSigA0とSigA1がACシグナリングをサポートしており、セル100によってACモードに切り替えられている場合の文字列は「SigA0、sigA1:AC_Select = 100」です。 関連する内部時定数を定義する文字列を含めることもできます。

IEEE 1149.6では、ACテストを開始する2つの新しい命令として、EXTEST_PULSEとEXTEST_TRAINが導入されました。特にテストするために一連のパルスが必要になる厄介なデバイスの場合、パルス試験は単一のパルスを送信させる好ましい方法です。 BSDLファイルには、関連するタイミング要件を提供するために、属性としてAIO_EXTEST_Pulse_Execution と、AIO_EXTEST_Train_Executionを含めることができます。

Compliance Pins コンプライアンスピン:

デバイス製造元は、ICがテストモード時のみ,JTAGピンがIEEE 1149.1規格をサポートするようにデバイスを設計する場合があります。たとえば,ICがノーマルモードの時には,JTAGピンを他の機能に割り当てたり,デバイスがJTAGコマンドを無視したりすることがあります。

規格では、このようなICは、強制的にIEEE1149.1準拠の動作をさせるために使用できる1つ以上のピンを持つ必要があります。このようなデバイスのBSDLファイルには、COMPLIANCE_PATTERNS属性が含まれ、機能を切り替えるためにこれらのピンに必要となるビットパターンを定義します。

バウンダリスキャンビットパターンを表すファイル形式

バウンダリスキャンテストが実行されると、シリアルデータシーケンスがJTAGデバイスのTDIピンにクロックインされます。 JTAG制御信号(TMS)を使用すると、これらのシーケンスでデバイスのステートマシンをさまざまな安定状態間で遷移させ、チェーンを通じてデータをスキャンすることができます。 SVFファイルは、これらのシーケンスをASCIIテキストで表現する1つの方法です。 それを使用するツールにとらわれずにファイルを作成できるので、デバイスのプログラムに使用されるファイルに適した形式で、データが異なるベンダーのツール間で転換される必要があるときにも活用されます。

SVFシーケンスは純粋にシーケンシャルであり、条件付きステートメントをサポートしていません。 したがって、ループを作成することは不可能であり、FORステートメントを使用するようなよく知られた構成はサポートされていないため、ファイルサイズが大きくなることがよくあります。 ただし、SVFファイルはデバイスプログラミングに適した媒体です。

これに代わる形式に、STAPL(Standard Test and Programming Language)があります。これは、アルテラが作成した初期のJAM™言語の標準化バージョンであり、JEDECのJESD-71標準に文書化されています。 STAPLでは、ループやその他のフロー制御が許可されているため、ファイルサイズが小さくなり、実行時間が短くなります。 また、デバイスのステータスのポーリングもサポートしているため、SVFファイルシーケンスにありがちな固定遅延はありません。

SVFファイルの中身

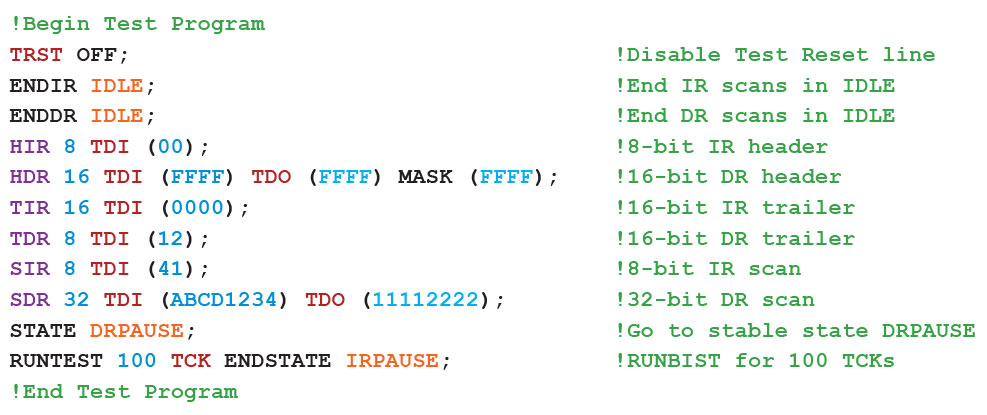

SVFは、Figure 6の例に示すように一連のコマンドで構成されています。このセクションでは、SVFファイルを構成する主なコマンドについて説明します。

Figure 6 – Example of a Simple SVF File

SVF Commands

主なSVFコマンドは次のとおりです。

- SIR(Scan Instruction Register):ターゲットデバイスの命令レジスタに適用されるシーケンスを指定します。 挿入する値(16進数)だけでなく、比較のためにTDOからの期待値を含めることもできます。 シーケンス内の特定のビットを無視する必要がある場合は、比較中に適用する必要があるマスクを含めることができます(たとえば、JTAGチェーン内の他のデバイスからのビットを許可することや、非同期クロックや浮動入力から発生するような予測不可能なビットを無視するために使用します)。

- ENDIR:命令レジスタのスキャンの終了時にステートマシンをそのままにする状態を指定します。 これらの状態は、IDLE、RESET、またはIRPAUSEです。 この例は、ENDIR IDLEです。

- SDR(Scan Data Register):他のターゲットレジスタに適用するテストパターンを指定します。 挿入される値(16進数)を含めるのと同様に、比較用のTDOの期待値と適用可能なマスクも含めることができます。

- ENDDR:データレジスタスキャンの終了時にステートマシンをそのままにする状態を指定します。 これらの状態は、IDLE、RESET、またはDRPAUSEです。

- STATE:このコマンドは、デバイスのステートマシンをある安定状態から別の安定状態に遷移させるために使用されます。中間状態を介した遷移を含む場合があります。 例えば、RESET状態を介してそのIDLE状態に進むには、ステートメントは次のようになります。STATE RESET IDLE。

- PIOMAP&PIO:SVFファイルは並列テストベクタを扱うことができ、PIOMAPコマンドはどのポートがそのように使用されているかを定義するために使用されます。 それぞれはそのシンボル名を使用して識別され、情報はピンの方向(入力、出力、または双方向)で提供されます。 たとえば、「PIOMAP(IN a IN b IN c)」はピンa、b、cをパラレル入力として定義します。 その後、PIOコマンドを使用して、適用するパラレルテストパターンを指定できます。たとえば、前のPIOMAPコマンドの後に「PIO(HLZ)」と入力すると、名前“a”のピンがハイレベルに設定されます。 ピン“ b”をローレベルに、ピン“ c”をハイインピーダンスにします。

- RUNTEST:デバイスのステートマシンを一定時間またはクロックパルス数の間、実行状態にします。

- TRST(テストリセット):オプションのテストリセット信号を制御します。

- FREQUENCY:それ以降使用される最大TCK周波数(Hz)を指定します。 このコマンドがfrequencyのパラメータなしで発生した場合は、全速に設定されます。

SVFファイルを使用して複数のJTAGデバイスのチェーンで操作を実行すると、ターゲットデバイスに関係のないシーケンス内のビットがいくつか存在します。たとえば、SIR命令では、最初にチェーン内のターゲットになっていないデバイスをBYPASSにシフトして、目的のデバイスのみに命令を実行させる必要があります。

JTAGチェーン長が長くなるにつれて、これらの追加のシーケンスを繰り返し挿入する必要があるため、SVFファイルが著しく増加する可能性があります。 これを最小限に抑えるために、ヘッダとトレーラを使用して、あらゆるスキャンシーケンスの開始または終了に適用されるビットパターンを定義することができます。 HDRコマンドとHIRコマンドは、データレジスタと命令レジスタのシーケンスの先頭にそれぞれシーケンスを自動的に追加するために使用されます。 同等のTDRコマンドとTIRコマンドは、後続シーケンスに対しても同じことを行います。

まとめ:BSDL、SVF、STAPLファイルの重要性

BSDLファイルはICのバウンダリスキャンアーキテクチャがどのように実装されているかを記述する媒体であり、バウンダリスキャンテストを実行する場合はそのファイルの入手が不可欠です。 これには、命令レジスタのサイズ、さまざまな命令に対応するバイナリコード、サポートされているオプションのコマンド、バウンダリレジスタで使用される各セルの詳細などの情報が含まれています。

これに対して、SVFファイルとSTAPLファイルはバウンダリスキャンテストの実行には必要ありませんが、特定のテストまたは機能を構成するステートマシンの遷移とビットパターンをリストする方法です。バウンダリスキャンはデバイスのプログラミングにも使用できるため、デバイス製造元のツールは多くの場合、インサーキットプログラミングの手段としてこれらのファイルを生成します。

バウンダリスキャンテストは、BGAの下などアクセスできない場所にあるものも含め、はんだ付けの欠陥を特定する強力な手段です。そして XJTAGのテストツールには、この記事で紹介してきた内容の詳細を知らなくても、テストを設計し実行できる直感的なユーザーインターフェースが提供されています。