XJTAGを使用したJTAGテスト

はじめに

JTAGを高い抽象度で扱うこと、リアクティブに(実行結果に応じて)テストパターンを生成する機能、及びデバイスセントリックという概念を導入することで、XJTAGはJTAGバウンダリスキャンテスト技術にイノベーションをもたらしました。

テストは電子回路実装基板の全ライフサイクルを通じて不可欠であり、BGAや他の同様のパッケージング技術の出現によって、JTAGがテスト技術の最前線に貢献するようになりました。

XJTAGは、テストシステム作成のプロセスをテスト実装の技術的詳細から抽象化しながら、JTAGの最大限の能力を引き出すように設計されています。

従来JTAGソリューションではJTAGデバイス間の接続テストを実装できますが、回路上にはまだ多くの非JTAGデバイスがあり、その多くはBGAパッケージを使用していて、これらは物理的にもJTAGを使ってもテスト出来ません。

これに対してXJTAGは、回路内のデバイスの現在のステータスを反映するために、テストの動作を調整します。したがって、非JTAGデバイスの多くを機能的にテストできます。

JTAGデバイス間の接続の完全性と、非JTAGデバイスの多くの機能をテストするXJTAGの能力は、1つ以上のJTAG対応デバイスを含む回路をテストするための貴重なツールになります。

XJTAGのテストは、JTAGバウンダリスキャンの技術に関する知識が無くても開発できます。XJTAGのベースであるデバイスセントリック手法は、回路を参照することなく、テスト対象のデバイスの観点でテストが構成されます。つまり、デバイスのデータシートを理解できれば誰でもXJTAGのテストを作成できるということです。

デバイスセントリック手法の優位性は、デバイス用に記述された一連のテストは、いつでも、どの回路でも使用できることです。そしてXJTAGには各種デバイス用のテストセットが付属していますので、テストコードをまったく実装することなくテストシステムを作成できます。

XJTAGを使用することで、設計の早期段階からフィールドサポートに至るまで、電子回路実装基板のテストやデバッグのプロセスを迅速、簡単、効率的にします。

設計段階

回路設計時にテスト容易化設計(DFT)の原則を意識することは重要です。XJTAGが公開しているテスト容易化設計ガイドラインを参考にすることで、すべてのデバイスがJTAG標準に準拠しているかどうかにかかわらず、テストカバレッジを最大限に引き出す究極の設計が出来るでしょう。

設計の検証

テストのプロセスは、最初の電子回路実装基板が製造される前に開始されます。設計が完了すれば、そのネットリストをXJTAGテストシステムのベースにすることができます。XJTAGは、ハードウェアが無くてもテストカバレッジのレポートを出力して、指定されたテストを実装するために必要なすべての接続が回路レイアウトによって提供されることを確認できます。

生産に先立って、回路レイアウトのテスト容易性をチェックすることにより、後工程で回路設計をやり直す際にかかる時間とコストを回避することができるでしょう。

回路のテスト

XJTAGのテストは、回路(またはJTAGチェーン全体)が完全に実装される前に開始できます。1つ以上のデバイスのJTAGチェーンが利用可能になるとすぐに、テストを開始できます。

XJTAGテストシステムの実行は、実装基板の完成が前提条件ではありません。それゆえ、より早い段階でテストやデバッグを開始して、障害を特定することで、設計サイクルを短縮します。XJTAGのデバイスセントリック手法なら、初期段階でテストを作成する際に行われた作業が無駄にならず、後でより完全な機能を備えたテストシステムの一部として簡単に変更することもできます。

回路のどの部分が実装されていても、テストのプロセスは同じです。

テストシステムを回路に接続する

テストを開始する前に、まずテストシステムを回路に接続する必要があります。XJLink は、PCのUSBインターフェースで高速JTAGアクセスを提供します。

各機能のライセンス情報はXJLinkのプローブ本体に書込まれるため、XJTAGテストシステムは利用場所を選びません。例えば、実験室でデスクトップPCを使用し、現場ではノートPCを用いることが出来ます。

XJLinkは、テスト対象基板に合わせて柔軟にJTAGのピン配置を設定する機能が有り、Multiice™ Xilinx™ Altera Byte Blaster™ 等の標準的なピン配置が選択可能です。また、標準的ではない他の特定のピン配置に設定することもできます。

XJLinkには、全機能を使用できるAPIも付属します。これにより、XJTAGハードウェアインターフェイスを使用して、独自のJTAG対応アプリケーションを作成することもできます。

JTAGチェーンの検証

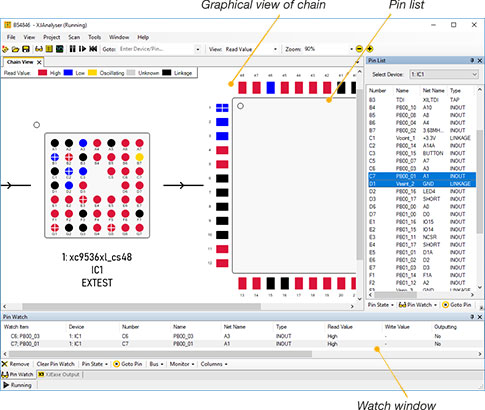

基板が用意できれば、XJTAGでJTAGチェーンの完全性を視覚的に確認できます。XJAnalyserは、回路のデバッグとJTAGチェーンの検証を、素早く容易にするグラフィカルツールです。

XJAnalyserプロジェクトの設定は、ウィザードを使用して、きわめて簡単です。

基板のJTAGに関する簡単な設定をするだけでXJAnalyserは、チェーン内の各デバイスからIDコードを抽出して、接続されているJTAGチェーンの完全性をチェックします。

有効なチェーンが確立されると、XJAnalyserは抽出されたIDコードから、適切なBSDLファイルを識別します。BSDLファイルには、各デバイスのバウンダリスキャンアーキテクチャがどのように実装されているかが記載されています。

XJAnalyserはプロジェクトベースのツールであるため、一旦プロジェクトが作成されると、必要に応じて保存および再利用できます。

図1は、2つのデバイスで構成されるJTAGチェーンを示すXJAnalyserのスクリーンショットです。これらのデバイスの1つは通常パッケージで、もう1つはBGAデバイスです。

ピンの色は現在の値を示しています。XJAnalyserは、出力ピンと双方向ピンの値を、ハイ、ロー、高速発振、低速発振に設定できます。

図1に示すように、XJAnalyserは回路内のピンに関する情報をデバイス毎に表示します(右側の領域のピンリスト)。また、選択したピンを表示(下側のピンウォッチ)することも可能です。これにより、関心のある特定の情報への直接アクセスが容易になります。

製造検証

JTAGチェーンの完全性が検証されたら、テストプロセスの次の段階は製造上の欠陥をチェックすることです。

図2 短絡の例

XJTAGの接続テストは、3種類の製造上の欠陥(短絡、断線、スタックの障害)を特定します。XJTAG独自の接続テストアルゴリズムは、高いカバレッジ率で、障害の正確な性質と場所を特定するように設計されています。

図2は、多くのJTAG接続テストで問題となる例を示します。従来の接続テストで用いられているアルゴリズムでは、Net CとDの間に示されるような単純な短絡を特定できても、Net AとBのインライン抵抗の短絡は検出されません。XJTAG接続テストアルゴリズムは、この問題を克服します。

XJTAGのテストは対象基板の現況にリアクティブに対応する能力があり、より改善された不良報告が得られます。不整合が発見された場合は、その不良箇所と原因を特定するために、より多くのテストを自動的に生成して実行します。

非JTAGデバイスの機能テスト

接続テストは最も効果的ですが、回路内のすべての接続をテストすることはできません。XJTAGのテストパターン生成技術はJTAGバウンダリスキャンテストの技術を最大限に活かして、あらゆる非JTAGデバイスの機能テストを可能にします。

図3に示すXJTAGテストシステムにおいて、非JTAGデバイスのテストは「XJEaseデバイスファイル」によって制御されます。これらデバイスファイルは、テスト対象デバイスごとに高級言語で実装されています。でも、特定回路にこれらテストを実装する情報は含まれていません。そのため、開発されたすべてのテストが同一プロジェクト、および他のプロジェクト間で、再利用可能です。

XJEngineは、デバイステストで実行するテストパターンを生成します。ピン値の設定に関してテストパターンが達成しなければならないことはデバイスファイルによって制御され、その要件を満たすテストパターンを作成するために必要な情報はプロジェクトファイルから取得されます。

これらのテストパターンはすべて、テストシステムの実行中に生成されます。これは、XJEngineが回路内のデバイスの現在のステータスを、XJEaseのデバイステストを制御するためにフィードバックできることを意味します。この情報は、XJEngineが生成すべき次のテストパターンをプログラムで制御するために使用されます。

図3 XJTAG テストシステム

プログラムに基づいた制御と、実行結果に応じてリアクティブにテストパターンを生成する機能をJTAGテストに採用することにより、テストできる回路の割合とデバイスの範囲の両方が拡大します。テストを有効にするために特定のモードにする必要があるデバイスがあれば、テストモードに入るために駆動する必要があるピンを、XJTAGテストシステムのXJEaseデバイステストに記述するだけです。その後、デバイスが所定の状態になったことを示す値がデバイスから読み取られるまで、繰り返しデバイスの状態を読みこみます。所定の値が読み取られれば、テストは次に進みます。この種のデバイスのテストは、回路とインタラクションするXJTAGの機能によってのみ実現可能です。

XJTAGにおける複数レベルの高度な抽象化により、テストシステムは極めて迅速に開発できます。

XJTAGのデバイスセントリック手法の核心である、回路実装からのデバイステストの抽象化には、2つの重要な利点があります。まず、テスト開発プロセスが極めて容易になりました。設定する必要があるピンと結果の値を記述するだけです。2つ目は、開発されたすべてのテストは、そのデバイスが使用される他の回路で再利用できて、回路のネットリストが変更されてもテストの修正は不要です。