JTAG – это нечто большее, чем просто отладка и перепрограммирование микросхем

Если Вы применяли какие-либо инструменты, использующие JTAG, то Вы уже знакомы с этим интерфейсом. Например, процессоры часто используют JTAG для доступа к своим отладочным функциям, также все ПЛИС используют JTAG для перепрограммирования.

JTAG – это НЕ ТОЛЬКО отладка процессоров.

JTAG – это НЕ ТОЛЬКО программирование ПЛИС/CPLD.

Название JTAG чаще всего ассоциируется с инструментами отладки и перепрограммирования микросхем. Однако, в этих инструментах реализована только часть возможностей JTAG.

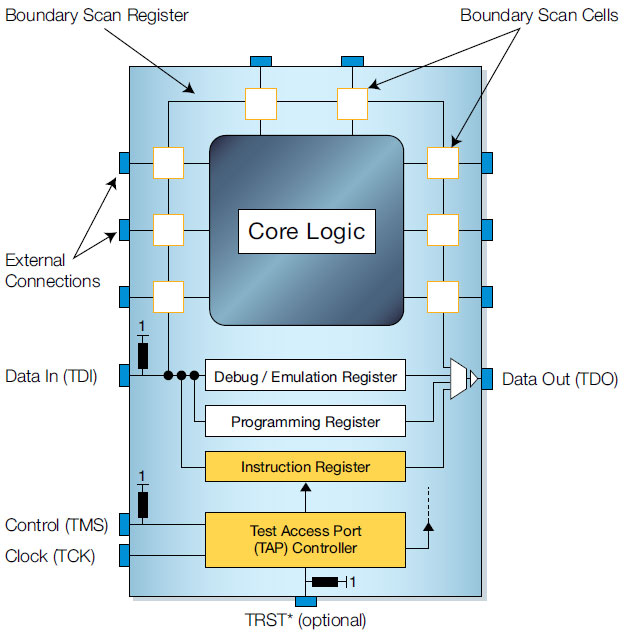

Эта часть возможностей, известная под названием Test Access Port или, сокращённо, TAP, является частью стандарта IEEE Std. 1149.1. Этот стандарт был разработан для тестирования сборок печатных плат (Printed Circuit Board Assemblies – PCBA) без необходимости доступа на так называемом “низком” (физическом) уровне, который требуется для анализа “сложных” случаев. Стандарт также не предусматривает разработку и использование специфических функциональных тестов. Изначально TAP был разработан только для взаимодействия с дополнительными регистрами, специально вставляемыми в микросхему с целью реализации данного метода тестирования.

Однако достаточно быстро производители микросхем заметили потенциал использования TAP и для других целей, например, для доступа к регистрам, предназначенным для отладки и перепрограммирования микросхем.

Теперь в микросхемы добавляется специальный регистр для тестирования через JTAG под названием Boundary Scan Register (BSR). Как и подразумевает название этого регистра, отдельные его части (или, по-другому, ячейки (Cells)) являются “пограничными” для микросхемы, так как располагаются между функциональным ядром и контактами корпуса микросхемы. По этой причине тестирование через JTAG часто называют пограничным сканированием (boundary scan).

Как технология пограничного сканирования, реализуемая стандартом JTAG, используется для тестирования печатных плат?

Ячейки регистра пограничного сканирования (Boundary Scan Register) могут работать в одном из двух режимов: 1) функциональный режим – ячейки не влияют на работу прибора, прибор работает в своём обычном виде; 2) тестирующий режим – ячейки отсоединяют функциональное ядро микросхемы от контактов корпуса. Тестирующий режим используется для управления значениями на контактах корпуса микросхемы (и в соответствующих цепях печатной платы), а также для считывания значений с подключённых цепей печатной платы.

Отключение функционального ядра микросхемы существенно упрощает разработку тестов, так как использование пограничного сканирования (boundary scan) позволяет не разрабатывать программу для микропроцессора или прошивку для ПЛИС и не включать прибор в “рабочем” режиме. Механизм управления и наблюдения за контактами корпуса микросхемы через четырёх-контактный TAP, JTAG интерфейс позволяет получить низкоуровневый доступ к контактам микросхемы для физического тестирования печатной платы.

Существует два способа тестирования печатной платы при помощи пограничного сканирования (boundary scan). Первый способ – тест соединений (connection test). Он даёт хорошее покрытие, особенно для поиска таких неисправностей, как замыкания. Этот способ использует только возможности микросхемы с поддержкой JTAG, при этом тестируются соединения (например, пропайки) и цепи, а в случае применения системы XJTAG, тестируются ещё и логические функции платы. Второй способ – использование микросхемы с поддержкой JTAG для взаимодействия с микросхемами без поддержки JTAG, такими как DDR RAM или Flash память.

Что такое тест соединений (connection test) через JTAG?

Тест соединений (connection test) проверяет, соответствует ли изготовленная печатная плата исходному проекту, а также наличие на ней не предусмотренных проектом разрывов цепей или лишних замыканий.

Если согласно проекту какие-то контакты микросхемы должны быть соединены где-то на плате, то можно проверить факт наличия соединения, подавая значения на один из контактов и считывая с других. Если согласно проекту контакты микросхемы НЕ соединены, то можно проверить, нет ли между ними лишнего замыкания, подавая на один из них значения и проверяя, что на остальные это не влияет.

Кроме того, тест соединений (connection test) позволяет обнаружить отсутствие нужных подтягивающих резисторов, и “залипания” сигналов. Это также делается путём выставления на контактах определённых значений и сравнения считанных значений с заданной таблицей истинности.

Система XJTAG на основе нетлиста печатной платы и информации, считанной с поддерживающих JTAG микросхем, полностью автоматически генерирует тестовые вектора для проведения теста соединений (connection test) всей платы.

Что же делать с остальными микросхемами на плате, которые не поддерживают JTAG?

Как правило, основные микросхемы на плате, такие как процессоры и ПЛИС, поддерживают JTAG, но существует множество вспомогательных микросхем, которые JTAG не поддерживают. Как пример можно привести такие микросхемы, как ЦАП, АЦП, DDR, SDRAM, SRAM, Flash, Ethernet контроллеры, температурные сенсоры, генераторы частот и многое другое.

Тест соединений (connection test) позволяет проводить тестирование на замыкания цепей между микросхемами с поддержкой JTAG и микросхемами без поддержки, при этом достигается хорошее покрытие. Однако протестировать обрывы в таких цепях уже не получится.

С целью тестирования на наличие обрывов цепей между микросхемами с поддержкой JTAG и микросхемами без таковой, требуется использовать так называемые функциональные тесты. Если функциональные тесты пройдены, то это означает, что обрывов быть не может. Функциональные тесты могут быть как очень простыми, например, включение светодиода и ожидание подтверждения от оператора, что светодиод действительно загорелся, так и посложнее, например, запись данных в память, считывание их же и сравнение считанных данных с ожидаемыми.

Насколько сложно подготовить JTAG тесты?

При помощи библиотеки тестов для стандартных микросхем без поддержки JTAG, поставляемой с системой XJTAG, возможна подготовка и запуск набора функциональных тестов без необходимости программирования. Библиотека тестов содержит тесты как для простых элементов, таких как резисторы и буферные элементы, так и для сложных микросхем, таких как память DDR3 и так далее.

Т.к. пограничное сканирование (boundary scan) отключает контакты корпуса микросхемы от функционального кремниевого ядра, единая тестовая модель может быть использована для управления периферийными микросхемами вне зависимости от того, какая микросхема с поддержкой JTAG использована.

Как правило, в печатную плату не требуется вносить никаких изменений, так как большинство плат уже содержат JTAG контакты для отладки процессоров или программирования ПЛИС.

Что ещё нужно для использования микросхем с поддержкой JTAG?

Для тестирования печатной платы при помощи пограничного сканирования (boundary scan) требуется для каждой микросхемы с поддержкой JTAG скачать с сайта производителя микросхемы так называемый BSDL-файл – Boundary Scan Description Language. Это текстовый файл, описывающий назначения ножек корпуса микросхемы.

Используется ли JTAG тестирование в основном на производстве?

Не совсем. Одним из важнейших преимуществ тестирования через пограничное сканирование (boundary scan) является тот факт, что из дополнительного оборудования требуется только JTAG контроллер. Другие технологии тестирования, такие как летающие щупы (flying probe), рентгеновское сканирование, многозондовое тестирование (bed-of-nails) и так далее требуют наличия дорогостоящего оборудования, которое не всегда доступно.

Использование пограничного сканирования (boundary scan) при первом тестировании позволяет проводить тестирование более уверенно, так как не требует включения платы в основной режим работы и даже может быть выполнено ещё до окончания разработки “прошивки”. Эти же тесты, разработанные при проектировании, могут быть использованы и на производстве.

Почему следует использовать пограничное сканирование через JTAG для тестирования печатных плат?

BGA

С увеличением доли микросхем, реализованных в корпусе BGA (Ball Grid Array), применение традиционных систем тестирования печатных плат, таких как многозондовое тестирование (bed-of-nails) или летающие щупы (flying probe) становится всё более ограниченным, так как “внутренние” контакты физически недоступны.

Пограничное сканирование (boundary scan) на основе JTAG при помощи простого “четырёхконтактного” интерфейса позволяет произвольно управлять контактами корпуса микросхемы с поддержкой JTAG, в том числе считывать значения, не имея к контактам физического доступа.

Стенд

В процессе проектирования и отладки временны́е и денежные затраты на разработку/приобретение испытательных/отладочных стендов могут быть очень существенными, а в некоторых случаях и превышать затраты на само проектирование. Во многих случаях использование пограничного сканирования (boundary scan) позволяет вообще отказаться от применения испытательного стенда, а в остальных случаях подойдет и значительно более простой и дешёвый стенд.

Малые партии

В случае, когда у компании имеется много проектов плат, выпускаемых малыми партиями, задача удешевления тестового оборудования особенно актуальна. Единственно приемлемым вариантом в данном случае является покупка системы “летающие щупы” (flying probe), но если цена при этом делится на все проекты, то временны́е затраты на подготовку теста для каждого проекта остаются неприемлемыми. Использование пограничного сканирования (boundary scan) позволяет ускорить подготовку теста для каждого проекта, при том, что покупка дорогостоящего тестового оборудования теперь не требуется.

Стоимость разработки теста

Так как разные микросхемы (процессоры и ПЛИС) взаимодействуют с периферией разными способами, разработка традиционного функционального теста отдельно для каждой платы является очень затратной. Пограничное сканирование (boundary scan) существенно сокращает стоимость разработки тестов благодаря упрощённому способу управления контактами корпуса микросхемы для взаимодействия с остальными компонентами на плате. А унифицированный интерфейс JTAG позволяет формировать отдельные тесты как библиотечные элементы и использовать их в разных проектах вне зависимости от применяемых микросхем с поддержкой JTAG.

И для тестирования и для программирования

JTAG часто применяется для программирования микросхем (ПЛИС) на плате в процессе производства. А если к программированию дополнительно добавить тестирование платы через так называемое пограничное сканирование (boundary scan), то получится существенно сэкономить время и упростить производство.

Использование на производстве тех же тестов, которые применялись при проектировании

Обычно для тестирования изделий на производстве применяется большое дорогостоящее оборудование. Всё, что требуется для применения пограничного сканирования (boundary scan) через JTAG – это контроллер XJLink, размерами сопоставимый с компьютерной мышью.

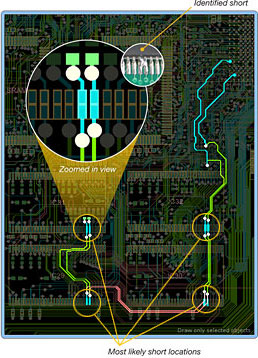

Удобная диагностика неисправностей

Пограничное сканирование (boundary scan) через JTAG, в отличие от специально разработанных функциональных тестов, позволяет получать информацию о точном месте возникновения неисправности, что очень помогает при восстановлении платы. А применение системы XJTAG ещё и позволяет визуализировать место неисправности на плате и указать точное место в принципиальной схеме.

Восстановление нерабочих плат, где функциональные тесты бессильны

Пограничное сканирование (boundary scan) через JTAG можно использовать на плате, где не работает ничего, кроме самого JTAG интерфейса. Если плата не включается, то провести традиционные функциональные тесты не получится. Простейшая неисправность в таких элементах на плате, как память или генератор синхросигнала не позволят применить функциональный тест, но легко обнаруживается при помощи JTAG.

Ещё статьи

Концепция применения JTAG

Посмотрите, на что способен JTAG (Английский)

Технические подробности JTAG

Обзор аппаратной реализации JTAG

Руководство по улучшению тестопригодности (DFT)

Рекомендации по улучшению покрытия платы тестами (Английский)

JTAG-тестирование при помощи XJTAG

Как XJTAG расширяет возможности JTAG (Английский)