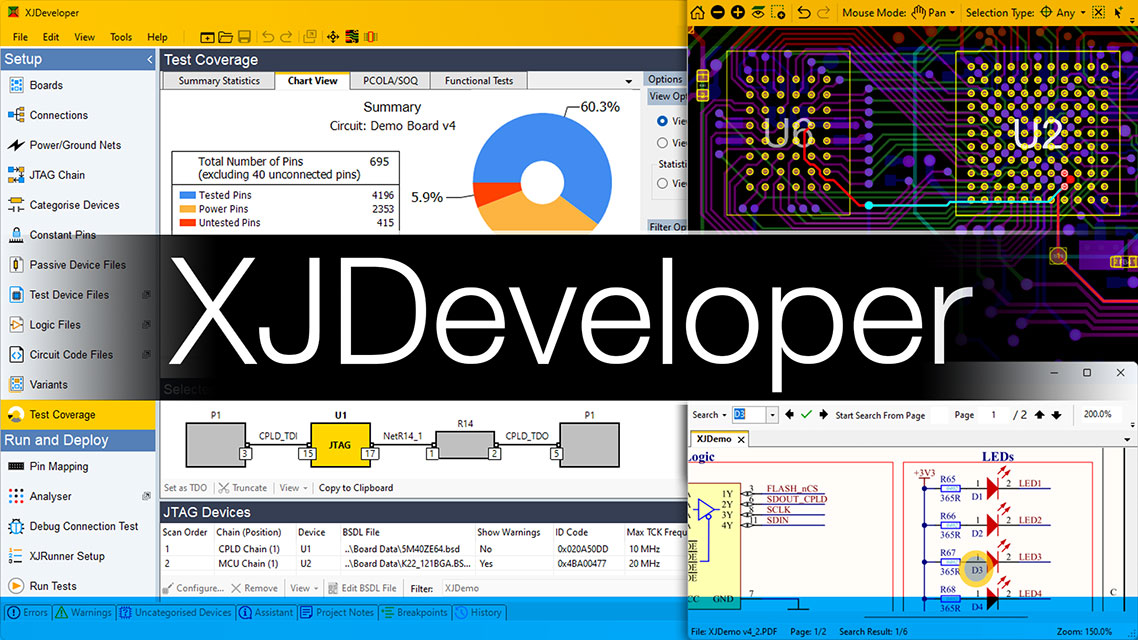

XJDeveloper — это программное приложение для визуальной отладки печатной платы через расположенные на плате микросхемы с поддержкой JTAG. Генерируемые автоматически тесты на обрывы/замыкания объединяются с тестами элементов, не поддерживающих JTAG, таких как микросхемы RAM и т.д., что позволяет провести всесторонний тест платы.Такие микросхемы, как Flash память, EEPROM, CPLD, FPGA и даже внутренняя Flash память микропроцессора, могут быть перепрограммированы при помощи системы XJTAG.

XJDeveloper может быть полезен в том числе и в процессе проектирования паты, когда ещё даже нет физического прототипа: встроенная система анализа полноты покрытия позволяет оценить процент покрытия будущей платы тестами.

Интуитивно понятный графический интерфейс с функцией drag & drop позволяет быстро и легко сформировать JTAG цепочку и классифицировать все устройства не поддерживающие JTAG. Все необходимые вспомогательные инструменты, такие как DFT анализ, Layout Viewer, Schematic Viewer и Netlist Explorer встроены в XJDeveloper.

Быстрая разработка тестов со встроенной библиотекой

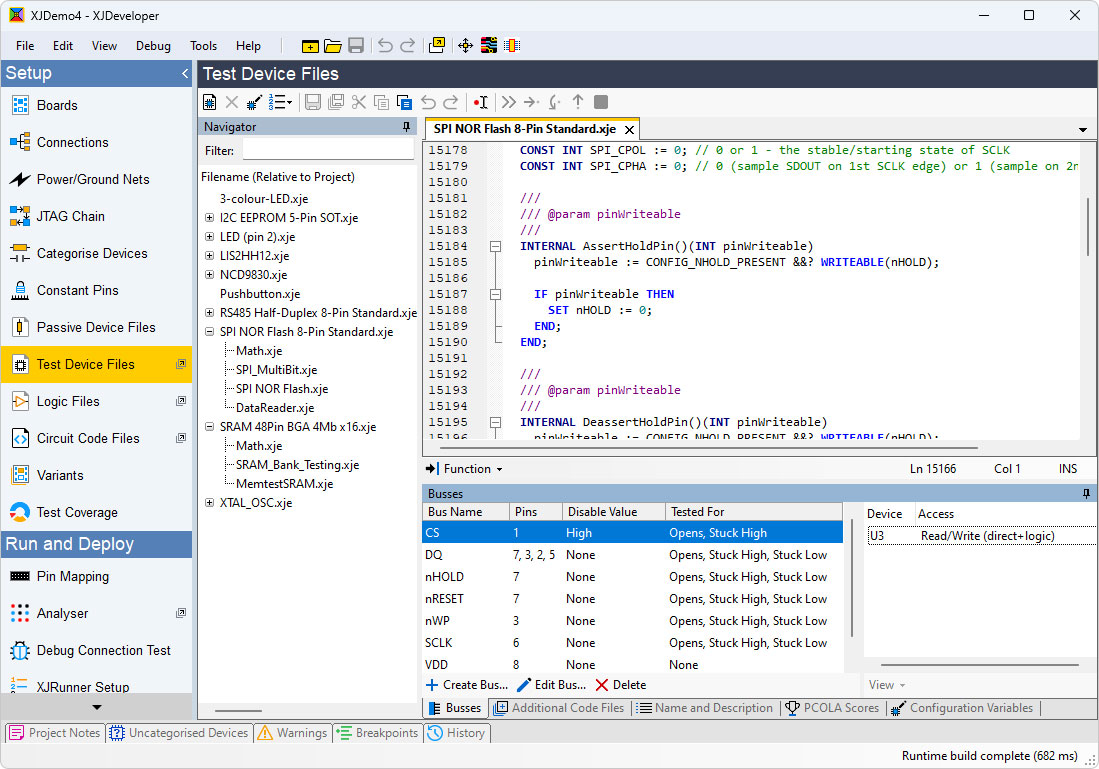

XJDeveloper помогает ускорить разработку тестов при помощи подсказок как классифицировать каждый конкретный элемент печатной платы. А если в наличии имеется BOM файл, то XJDeveloper ещё и подскажет, какую тестовую модель из имеющихся во встроенной библиотеке потенциально можно применить к каждому элементу.

Модели, содержащиеся во встроенных библиотеках, подразделяются на модели для простых пассивных элементов, таких как резисторы и т.д., модели для сложных микросхем, таких как DDR3 и т.д., и модели для элементов, работу которых можно описать таблицей истинности, таких как буферные элементы и логические вентили.

Используя эти модели, собрать полнофункциональный тест платы можно без дополнительного программирования.

Тест на обрывы / замыкания

В XJDeveloper встроен так называемый connection test, т.е. автоматический тест на обрывы/замыкания всех цепей, доступных через микросхемы, входящие в JTAG цепь. Этот тест идентифицирует большой диапазон такого рода неисправностей, как например, ошибочное подключение, подключение к питанию или “земле”, резистивные замыкания (resistive shorts), инверсные замыкания (inverted shorts) и т.д. Подтягивающие (Pull-up и Pull-down) резисторы также идентифицируются. XJDeveloper позволяет тестировать намного больший процент схем, чем другие JTAG решения.

Автоматический тест на обрывы/замыкания также тестирует как управляющие сигналы, так и сигналы данных на таких логических элементах, как буферные элементы и логические вентили.

В случае обнаружения неисправности, автоматический тест на обрывы/замыкания генерирует серию целевых тестовых воздействий с целью выявления точного местоположения неисправности.

Тестирование не-JTAG компонентов

XJDeveloper существенно упрощает использование компонентов из JTAG цепи для тестирования компонентов, не имеющих JTAG интерфейса. Например, при тестировании памяти путём записи и чтения данных, нет необходимости запускать процессор и готовить для него соответствующую программу. И даже такие сложные тесты, как отправка и приём Ethernet пакетов, могут быть выполнены как часть общего процесса тестирования платы. XJDeveloper может быть использован для тестирования или программирования Flash, все типы памяти, FIFO массивы, устройства IIC и SPI.

Импорт стандартных данных

Для тестирования цепей вокруг JTAG компонентов, XJDeveloper использует стандартные нетлисты схем и BSDL файлы (Boundary Scan Description Language). Поддерживается около 80 форматов нетлистов. Один из этих форматов, а именно ODB++, кроме информации о цепях, может также содержать топологию платы, что позволяет показать физическое место расположения неисправностей.

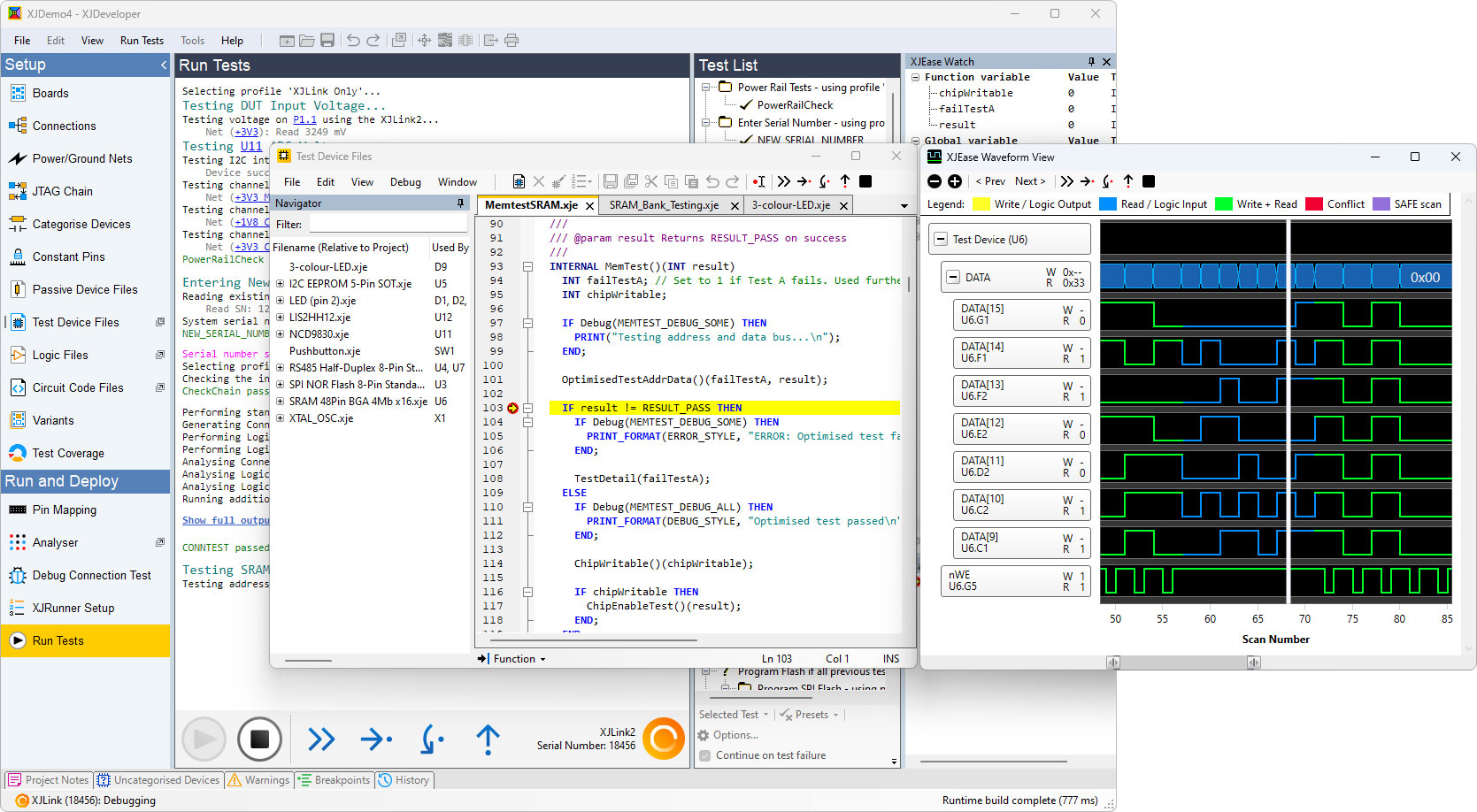

XJEase — Язык описания тестов

Встроенный в XJDeveloper язык высокого уровня под названием XJEase является очень функциональным и гибким инструментом достижения задач, поставленных перед тестированием компонентов не имеющих интерфейса JTAG.

Встроенная библиотека содержит тесты на тысячи компонентов, является пополняемой и позволяет легко сконструировать тест для нового компонента, даже без опыта программирования. Вот пример кода на XJEase.

Использование возможностей полнофункционального языка высокого уровня, таких как переменные, циклы, условные операторы, функции и т.д., позволяет сформировать не только “пассивный” тест (сигнал-ответ), но и разработать тест, взаимодействующий с платой в режиме реального времени, например, ждущий нажатия кнопки на плате.

Инструменты отладки, такие как окно просмотра значений переменных, точки прерывания и т.д., позволяют подготовить новый тест максимально быстро.

Компонентно-ориентированний — многоразовый тест

Тесты пишутся в терминах тестируемых компонентов, т.е. всё, что требуется от разработчика тестов, это указать, на какие пины тестируемой не-JTAG микросхемы подать какие значения, а с каких считать. Система автоматически сформирует все необходимые JTAG команды.

Такой подход позволяет не только ускорить разработку самого теста, но и позволяет повторно использовать один и то же тест для тестирования нескольких одинаковых микросхем.

Перепрограммирование Flash памяти и JTAG компонентов

Во встроенной библиотеке присутствуют все необходимые файлы для загрузки данных во Flash память из образа. Для перепрограммирования таких JTAG компонентов, как CPLD и FPGA, XJDeveloper позволяет запустить STAPL / JAM или SVF файлы, сгенерированные инструментами от разработчиков этих ПЛИС. Внутренняя Flash память некоторых микропроцессоров также может быть перепрограммирована через JTAG интерфейс.

Анализ полноты покрытия

Как только в процессе проектирования была закончена разработка принципиальной схемы и появилась возможность экспортировать нетлист, можно заводить проект в XJDeveloper и начинать прикидывать возможную полноту покрытия тестами. Рассчитываемая автоматически полнота покрытия учитывает как автоматические тесты на обрывы/замыкания, так и библиотечные тесты компонентов без JTAG.

На сайте xjtag.com можно скачать руководство с рекомендациями по повышению полноты покрытия, что позволит избежать многих потенциальных проблем. Руководство называется XJTAG’s Design For Test (DFT).

Встроенные XJRunner, XJAnalyser, Schematic и Layout Viewer

Тесты, разработанные для массового тестирования на производстве, перед отправлением на фабрику могут быть отлажены во встроенном XJRunner. А встроенные инструменты просмотра схемы и топологии помогут быстро найти нужный компонент или место расположения неисправности. Подробнее о XJRunner, XJAnalyser, Layout Viewer и Schematic Viewer на отдельных листах.

Интеграция

Тесты XJDeveloper могут быть интегрированы в NI LabVIEW™. Специфические тесты также могут быть разработаны на Visual Basic®, C#® и т.д., а также с использованием .NET интерфейса.

Разработка тестов

Если все инженеры очень сильно заняты работой, компания XJTAG предлагает разработать своими силами тест как всей системы, так и тесты для отдельных специфических микросхем.

Нет нетлиста? Не проблема!

Даже если нетлист платы отсутствует, плата всё равно может быть протестирована. Функция тестирования платы без нетлиста позволяет получить необходимую информацию из BSDL файлов. Система автоматически найдёт компоненты в JTAG цепи, а компоненты без JTAG, такие как RAM или Flash память, могут быть при необходимости указаны вручную.

Возможности

- Автоматическое тестирование на обрывы/замыкания

Достигает наибольшего процента покрытия по сравнению с аналогичными системами и локализует неисправность с высокой точностью. - Тестирование и программирование компонентов, не поддерживающих JTAG

Компонентами без поддержки JTAG, подключенными к компонентам из JTAG цепи, можно управлять так же просто, как если бы они были частью JTAG-цепи. - Гибкий высокоуровневый язык описания тестов

Специально разработан для удобного описания процесса тестирования. - Компонентно-ориентированный подход

Тесты компонентов могут быть многократно использованы в различных проектах без каких-либо модификаций. - Исполнение тестов по высокоуровневым условиям

Исполнение каждого конкретного теста может быть поставлено в зависимость от конфигурации платы и/или результатов прошедших тестов и/или прочих условий. - Встроенная библиотека тестов

При инсталляции дистрибутива XJTAG также устанавливается большая библиотека тестов, хранящихся в виде исходных кодов на языке XJEase. - Layout Viewer — Отображение топологии платы с указанием на компоненты и неисправные трассы.

- Schematic Viewer — Отображение принципиальной схемы в процессе отладки.

- Реализация тестов максимально открыта

Данные, формируемые в процессе автоматического тестирования на обрывы/замыкания, доступны для просмотра, а библиотека готовых тестов хранится в исходниках. - Диаграммы сигналов (Waveform)

Работу тестируемой платы можно сохранить в виде диаграмм сигналов как при запуске скриптовых тестов, так и при пассивном наблюдении в окне Analyser. - Отладка тестов на языке XJEase

Отладчик позволяет проводить пошаговое выполнение, уставить точки прерывания, выводить значения переменных. - Не требуется детальных знаний о работе JTAG

Пользователь XJTAG описывает тесты в понятном человеку виде, а всё взаимодействие с интерфейсом JTAG система XJTAG берёт на себя. - Внутрисистемное программирование компонентов

Программирование компонентов, установленных на плате, возможно как через графический интерфейс XJDeveloper с использованием файлов SVF и STAPL, так и непосредственно из скрипта XJEase. - Тестирование при отсутствии нетлиста

Запуск как автоматического теста на обрывы/замыкания, так и библиотечных тестов возможен даже при отсутствии нетлиста тестируемой платы. - Экспорт проектов в формат XJRunner

Проект тестирования упакованный в формат XJRunner защищён от модификаций тестов, что позволяет развернуть тестирование на производстве без лишних опасений. - Анализ полноты покрытия тестами

XJDeveloper формирует отчёт, показывающий покрытие элементов платы тестами всего проекта тестирования. - Поддержка 1149.6

Поддерживаются компоненты, работающие в соответствии со стандартами 1149.1 и 1149.6.

Часто задаваемые вопросы

General

What is included with XJDeveloper?

XJDeveloper includes:

- Test development capabilities

- BSDL file editor/viewer

- JTAG Chain Debugger and signal integrity testing

- Library of non-JTAG testable devices

- Library of logic devices and truth tables

- XJEase language – ability for user to create new tests/modify library tests

- XJEase software debugger

- Ability for user to add connections/remove connections from netlist

- Schematic viewer

- Layout viewer

- Waveform viewer

- XJRunner – integrated in XJDeveloper and as separate XJRunner application

- XJDemo board & tutorials

What options are available with XJDeveloper?

- XJDeveloper is available with or without XJAnalyser functionality.

- XJDeveloper is available with or without XJFlash test generation capability.

- XJDeveloper can work with hardware licensing or with network licensing.

Technical questions

What files / data do I need to start working with XJDeveloper?

The minimum needed is the BSDL file for at least one of your JTAG devices (available from the device manufacturer).

Results will be much better and test coverage easier to achieve if you have a netlist for the board you wish to test. This is usually exported from the board design (EDA) tools.

If your EDA tools support export in ODB++ format, by using this as the netlist, XJDeveloper will also have access to layout information on your board to improve how it shows you problems.

If you have a Bill of Materials (BoM) for your design, XJDeveloper can use the information in it to help you improve your setup and save time in deciding how to categorise devices.

Providing the schematics (in PDF format) to XJDeveloper also allows it to help better during board setup.

You do not need the board you wish to test in order start the setup, though you will want to verify your tests on real hardware at some stage.

What netlist formats does XJDeveloper support?

Our recommendation is that customers use ODB++ board data because this contains both netlist and layout information and almost all CAD tools can generate ODB++. However, XJDeveloper supports over 100 formats of netlist, so if you do not have ODB++ we simply suggest you try using yours. If XJDeveloper does not recognise it please send it to us, we will gladly convert it to one that we can support, and we will also add support for your format into the next release of XJTAG software.

Can I update the netlist on an existing project?

Yes, simply edit the board to use the new netlist. XJTAG will migrate all the existing setup to the new netlist.

I have modified the board during bring-up – can I represent this in XJTAG?

XJTAG has the ability to add connections (e.g. wire mods) to the circuit model, or to disconnect parts of the circuit (e.g. cut tracks) in addition to being able to mark devices such as resistors and connectors as fitted or unfitted.

How easy is it to write my own tests?

We think it is very easy. But mostly you won’t have to, because the XJEase library contains a large number of common devices such as RAM, Flash, etc.

The XJEase language is designed so that you work by thinking about the device you are testing, so if for example you want to set the nOE pin high on a chip, that is how it is described in XJEase (SET nOE := 1; ) No need to worry which JTAG device the pin is connected to, or how it is connected, XJTAG works that out for you.

The XJEase language means you can do more than just play back a pre-defined set of vectors – you can use IF or WHILE statements to make decisions during tests, and even call other programs from within the tests.

The library of tests provided with XJEase contains a wide selection of devices, and you can see all of the XJEase source code for these tests. So if you want to find out how to do something for a new device, look in the tests we supply for a similar device, and copy or modify it.

The XJEase library also contains functions for using protocols such as I2C or SPI, and useful functions for tasks such as reading programming information from files in various formats, doing maths operations, etc.

What test coverage can I get using XJTAG tools?

The best answer we can give is to suggest you try XJTAG and let XJDeveloper generate a test coverage report for your circuit. XJDeveloper can also give some indications of parts of the board which are not tested or for which testing could be improved.

If you would like to take advantage of a free DFT Coverage Review of your initial design, our experienced test engineers will be happy to provide an analysis of boundary scan testability and make suggestions for improvements to maximise test coverage. Contact us now.

System requirements

Рекомендованные системные требования

- Процессор Intel® Core i3, i5, i7 или эквивалентный (любого поколения)

- Microsoft® Windows® 10 1607 и новее (32 или 64 бит), или Windows 11

- 8 Гб оперативной памяти

Upgrades / Support / Maintenance

Can I upgrade to add XJAnalyser or XJFlash later?

Yes, upgrading is simple and our costs are transparent with no penalty for adding functionality at a later date.

What support does XJTAG offer?

Customers with a support + maintenance agreement have access to both bug-fix software releases and new-feature releases. XJTAG offers support by email and online meetings during UK office hours.

Where appropriate we will offer an online meeting to view problems directly on a customer’s PC, or to demonstrate the use of a feature by showing a PC desktop to the customer.

In the event of a fault developing in XJTAG’s hardware XJTAG will replace or repair the unit and will work with the customer to minimise downtime (e.g. by loaning a unit during the repair).

Free evaluation / Licensing

What are the differences between the trial version and the purchased product?

There is no difference between the functionality of the purchased product and the free evaluation version. We provide full technical support by telephone and email, to help with the set-up or troubleshoot any issues during your trial. You will also have access to XJTAG’s device test libraries and latest software upgrades, during your 30-day evaluation period.

Can I convert my trial version to a purchased product?

Yes. If you already have XJDeveloper for evaluation, you can continue using it without interruption by purchasing the full licence. Contact your XJTAG distributor to make a purchase and have your licence extended.

- Проектирование и отладка тестов

- Подготовка внутрисистемного программирования

- Анализ полноты покрытия тестами

- Встроенная библиотека тестов микросхем без поддержки JTAG

Выгоды

- Сокращение общего времени отладки плат

- Удешевление проекта за счёт выявления потенциальных проблем на более ранних стадиях проектирования

- Сокращение времени разработки тестов за счёт повторного использования наработок, полученных на производстве и при обслуживании

- Сокращение времени разработки тестов за счёт повторного использования одних и тех же наработок в разных проектах

Гибкие возможности лицензирования

- Аппаратная лицензия

– встроена в JTAG контроллер, что позволяет инсталлировать систему XJTAG на неограниченном числе компьютеров - Сетевая лицензия

– хранится в лицензионном сервере и доступна в любой точке мира, где есть интернет

Получить дополнительную информацию, а также запросить цены и демонстрационный комплект можно у локального дистрибьютора.