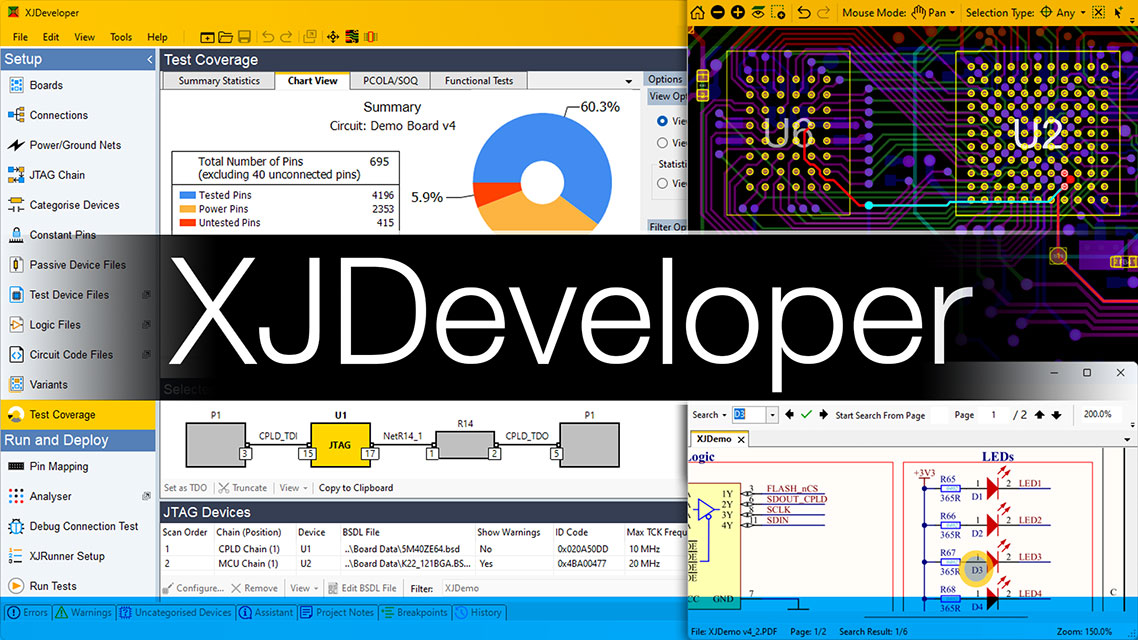

XJDeveloper — 先进的图形界面

XJDeveloper是简单快速地安装和测试的图形化工具。在制造过程中,随着XJDeveloper 通过在产品设计中书写的脚本的重复使用,可缩短产品上市的时间。

一个内嵌的连接性测试,结合非JTAG的XJEase,核对电路板的短路开路故障。使用XJDeveloper可简单创建或是定制测试。通过DFT分析可以查看电路板的测试覆盖率,同时内置了网络表浏览器,Layout Viewer,Schematic Viewer提供简单的界面,查看器件之间的连接性。

XJDeveloper 可用于JTAG器件(例如CPLD,FPGA)与非JTAG器件(例如 EEPROM,Flash)之间的编程 。

- 开发&调试测试

- 在线烧写设置

- 测试覆盖率分析

- 非JTAG器件库

主要优点

- 由于高精度的故障隔离,从而缩短了调试板子的时间。

- 提高您的产品上市时间,降低您的项目风险的早期设计验证

- 在制造和现场支持时,通过重用原型/设计的测试,可降低这个测试开发时间

- 通过测试重用,可跨越项目,并能连续不断的节省时间

灵活的授权许可选项

- 硬件许可

–保存在JTAG控制器中,这样您可以在任意数量的电脑上使用XJTAG - 网络许可

–保存在一个联网的许可服务器上,可以从世界上任何地方访问

高级连接测试

作为脚本的一部分,一个拥有专利的连接测试能在板上运行。通过利用板上器件的特征和内连关系的知识,XJTAG能够实现比其它JTAG系统更高的测试精度。

通过监控器件案的状态,XJTAG还可以对发现的任何故障提供有关定位和故障的精确特征的更多信息。除此以外,输出信息中还包含了一些可点击的链接,使故障非常容易地就能在Schematic Viewer和Layout Viewer中显示出来。

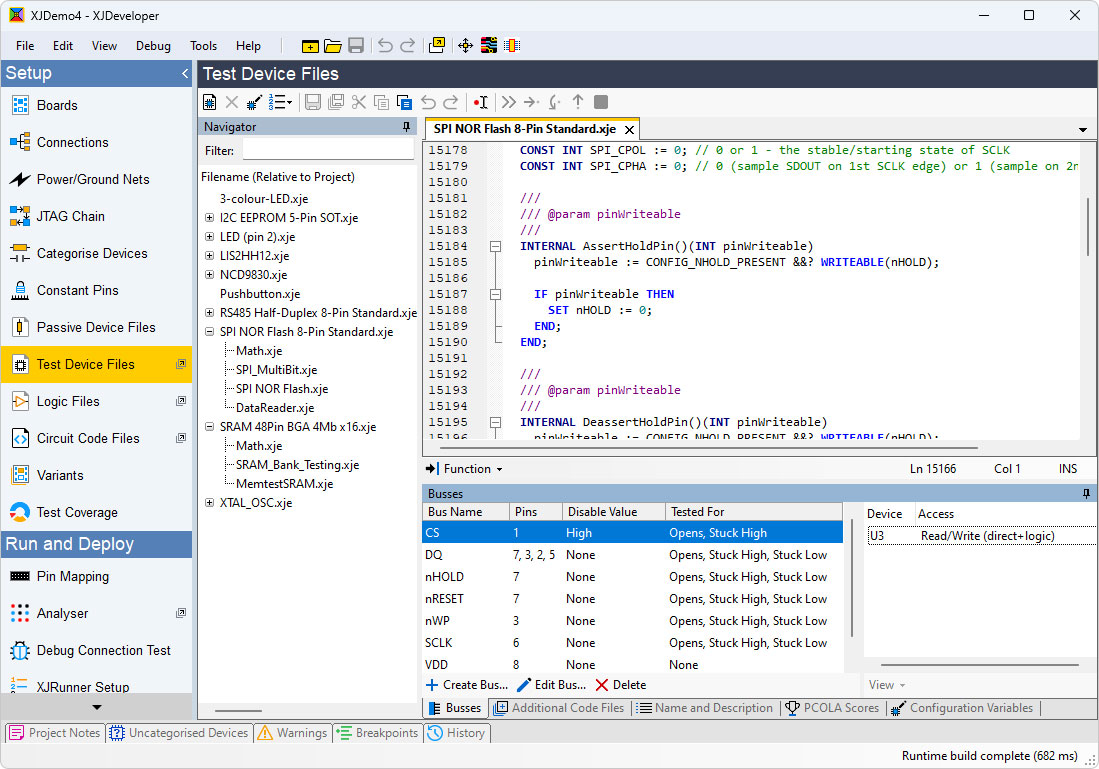

免费器件测试库

安装XJEase库包含测试上千个设备,包括Flash和其它器件编程的实例。即使用户从未使用过XJTAG,无需额外的编程,建立一个完整的测试工程也是可能的。

用户如果不能找到你特定的器件文件,可以下载相似器件的文件,并稍微改动一下满足要求。同时,我们也将提供这个方面的服务,满足用户的要求。这里提供一个XJEase代码例子

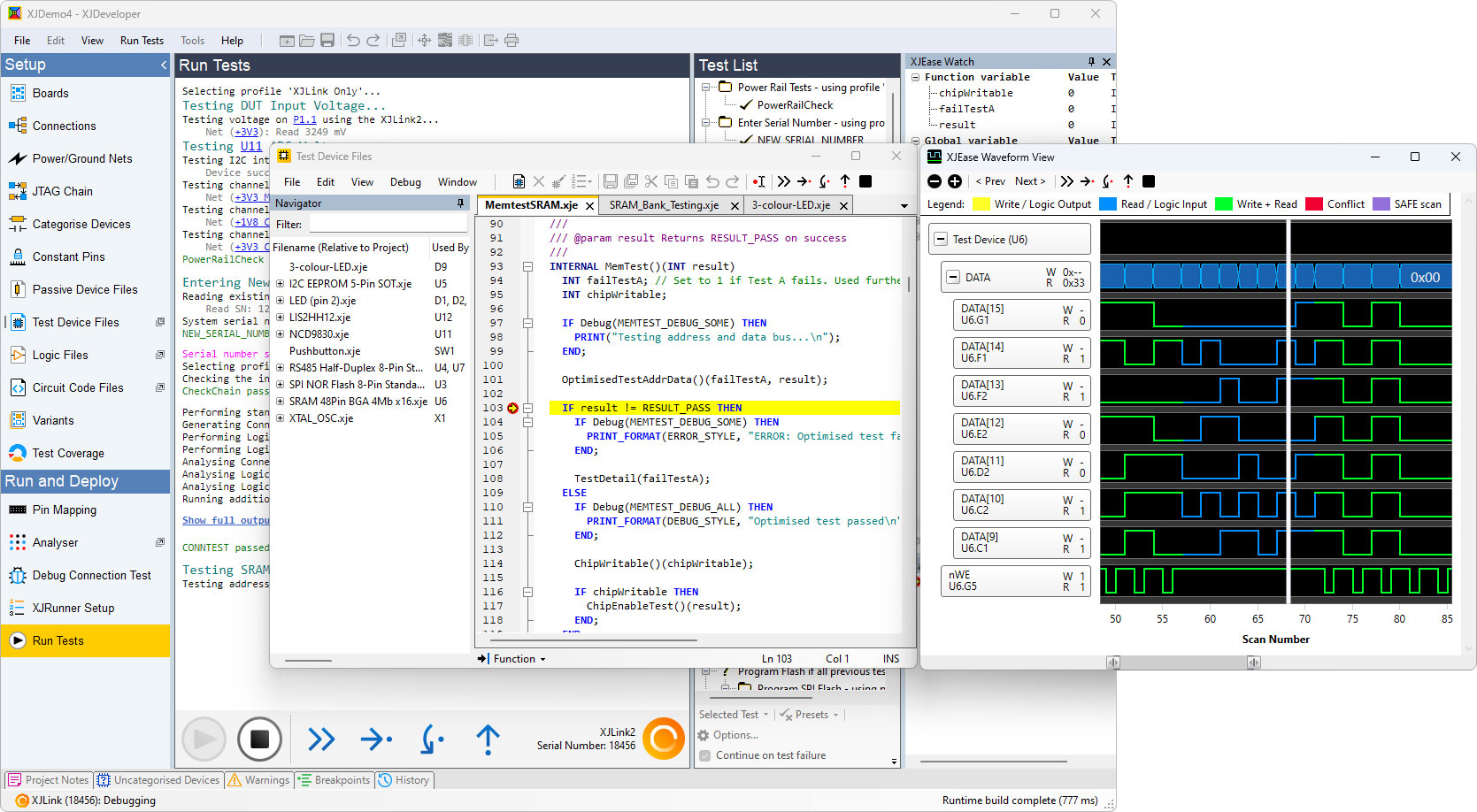

XJEase — 灵活的、高级的、测试描述语言

具备一个编程语言的所有优点和灵活性,如循环、变量、流程控制,这些都可用于描述器件和电路的测试。在XJEase程序的控制下,通过生成要求的测试序列,XJTAG可以很容易地实现其它JTAG系统无法实现的复杂的测试。

XJDeveloper contains a software debugger for use during XJEase development and prototyping.

This debugger allows you to:

- 单步运行;

- 设置或删除断点;

- 检查和设置变量值;

无需了解JTAG工作机理

如果您不得不创建您的测试,XJDeveloper也可让您的工作变得容易,XJEase已经对器件测试时创建测试向量并实施这些测试的细节进行了抽象,这意味着开发非JTAG器件的测试时简单快捷的。

XJDeveloper将检查待测的器件引脚是否在JTAG器件可访问的网络上,并且JTAG器件引脚必须是可听从控制去访问正确的网络。

而且,一旦您有某个器件的测试文件,只要电路板上有该器件,您就可重用这些文件。

多板测试

测试多板和测试单个板一样容易。只要把网表提供给XJTAG,并且告诉它这些板的相互连接关系,其它事情就交由XJTAG的运行引擎去处理。

运行测试

从XJDeveloper内部可以直接运行测试脚本。当然您也可以根据需要用其它方法运行测试脚本。

XJRunner是生产/服务环境下运行阶段的解决方案,是专门为生产和服务环境设计的,包含有额外的日志、序列码和用户管理功能。它有命令行和图形界面两个版本,以便将XJTAG与其它测试系统集成。

网表

能被XJTAG自动识别的网表格式包括: EDIF 2 0 0, RINF, Protel, PADS-PCB, Cadence Allegro, P-CAD, Genrad, BoardStation (Mentor), Zuken, Protel V2 和100多种格式。如果不能识别用户的网络表格式,我们将帮助转换并为用户提供未来版本的支持。XJTAG Support。

Testing with no netlist

If you don’t have the netlist for a board you need to test, XJDeveloper allows you to base a test system on the BSDL files for the JTAG devices on the board rather than forcing you to use a netlist. The system can then automatically learn from a golden board the connections between the JTAG devices for use during connection test. You can also add additional non-JTAG device such as RAM, flash or devices on peripheral busses such as I²C and SPI, in order to extend the test coverage.

特征

- 高级连接测试

有比大多其它JTAG解决方案更高的测试成功率和提供高精度的故障隔离。 - 灵活的、高级的、测试描述语言 简化创建测试的处理

- 以器件为中心的方法

器件测试可以无需修改在不同的电路板上重用。 - 测试和编程非JTAG器件

可以测试和编程连接到链上JTAG器件的非JTAG器件,实现高级测试-例如以太网回环。 - 免费器件测试库

安装XJEase库包含测试上千个设备。 - 无需了解JTAG的工作机理

XJTAG 系统操作将如何驱动JTAG 链。 - 器件编程

通过XJEase可用SVF和STAPL文件对器件进行编程,或者用XJDeveloper脚本对器件直接编程。 - Layout Viewer(布局查看器) 让你可以快速找到器件、网络和管脚在电路板上的实际位置。

- XJTAG原理图浏览器 来快速了解电路中正在使用的设备,以帮助识别故障和调试测试。

- 集成自定义应用程序,来创建整个测试系统。

- 支持 1149.1 和 1149.6 器件标准

XJTAG系统任何部分的报价或支持,请联系您当地的经销商。